现场可编程门阵列的供电

时间:03-24

来源:互联网

点击:

ADP2114同步降压开关稳压器

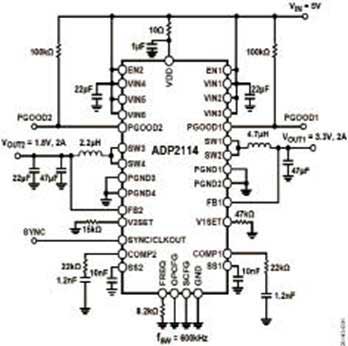

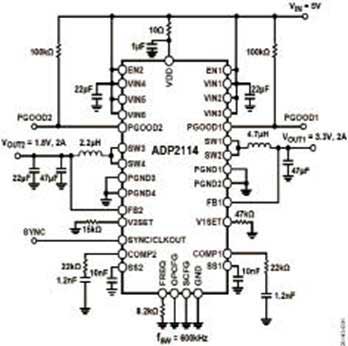

ADP2114(图4)是一款功能多样的同步降压开关稳压器,可满足各种客户负载点要求。两个PWM通道既可以配置为分别提供2A和2A(或3A/1A)电流的两路独立输出,也可以配置为提供4A电流的单路交错式输出。ADP2114可提供高功效,开关频率最高可达2MHz。在轻负载时,该器件可以设置为脉冲跳跃模式工作,以便提高功效,或者设置为强制PWM模式工作,以便降低电磁干扰(EMI)。ADP2114还具有欠压闭锁(UVLO)、迟滞、软启动和电源正常输出指示等特性;保护特性有输出短路保护和热关断等。可以利用极小电阻和电容对输出电压、电流限制、开关频率、脉冲跳跃工作模式和软启动时间进行外部编程。

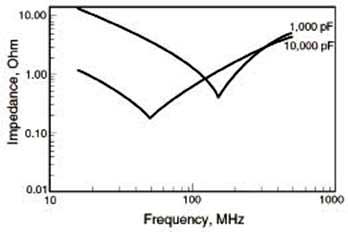

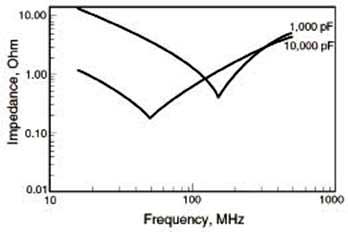

图3 电容阻抗随频率的变化曲线

图4 ADP2114同步降压开关稳压器

该器件可用于多个终端市场,例如通信基础设施、工业和仪器仪表、医疗保健以及高端消费电子市场。在这些终端市场的主要应用是分布式电源系统中的负载点稳压器。

虽然DC- DC稳压器的功效远高于LDO,但通常认为其噪声太高,无法在不显著降低其它参数性能的情况下,直接为高性能模数转换器供电。模数转换器的噪声至少有两个来源:通过电源纹波直接耦合至转换器中的噪声,以及磁耦合效益引起的噪声。

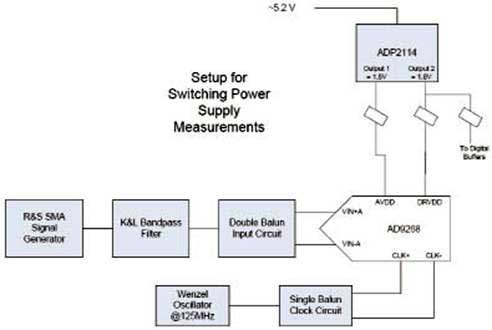

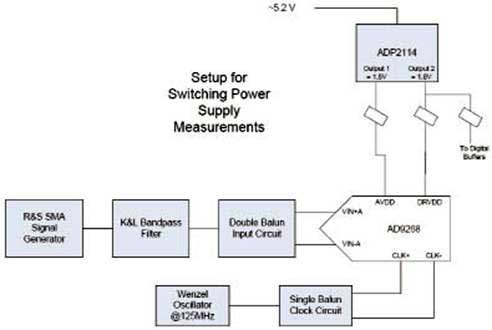

图5所示为一种实验室设置,针对采用低噪声LDO供电和采用开关稳压器ADP2114供电两种情况,比较一个16位、125MSPS模数转换器的性能。评估所用的AD9268可实现非常低的噪声,信噪比(SNR)为 78dB。DC-DC转换器贡献的额外噪声或杂散成分很容易反映在该模数转换器的输出频谱中,因此-152dBm/Hz的低本底噪声使它非常适合评估开关电源。

图5 开关电源供电测试

我们将ADP2114与低噪声LDO稳压器进行比较。高性能、16位、125MSPS AD转换器AD9268的评估结果表明:采用开关稳压器ADP2114供电与采用低噪声LDO稳压器供电相比,性能未受影响。

因此,ADP2114可以为用户提供可配置能力、多样化功能和灵活性,并且具有低噪声特性和高转换效率。同时能够满足各种客户负载点电源要求,性价比高,是 FPGA、ASIC、DSP和微处理器供电的理想选择。ADI公司提供网络工具可方便设计导入,同时提供评估板,有助于实现快速导入。

更多详细内容,敬请登陆中电网在线座谈网址:http://seminar.eccn.com

问答选编

问:印刷电路板中大电流供电,除加宽导电铜箔外,是否需要进一步采取镀锡等措施?

答:加镀锡一定程度上可以加大散热面积,但是效果不一定特别明显,最好还是加宽加厚导电铜箔。

问:在供电时,如果没考虑上电顺序,对整个系统的运行会有什么影响?

答:这个问题要针对系统的各个功能模块对上电的要求,如果系统中的某些电路对上电有严格的顺序,没有考虑到的话,很可能导致系统不工作。

问:电源纹波对FPGA性能有何影响?

答:工作时期的电源纹波要求、供电系统的压降、电源通路的等效阻抗设计等参数都是用户要特别留意的。建议在做大设计的时候一定要做电源完整性仿真,且要严格满足设计约束。

问:在IPTV系统中的FPGA供电电源有什么要求吗?

答:IPTV系统中FPGA的电源需求比较复杂,多达三种供电要求:内核电压、I/O电压和辅助电压。为了实现可靠的系统性,必须对这些排序,需要用电压管理芯片。

问:I/O 是否可以承受5V电压?

答:这个取决于I/O的供电电压。如果数字部分是5V供电,那么就可以。

问:ADP2118的输出电感和电容如何选择?它和负载电流、缓升时间有多大关系?

答:ADP2118为内部补偿器件,因此对输出电感电容有一定的限制,输出电容一般不能小于47uF,输出电感建议为0.8~3.3uH(针对频率设置为1.4MHz)、1.5~3.3uH(针对频率设置为700kHz)。输出电感电容的选择和负载电流、软启动时间并无太大关系。

问:ADP2114的PWM频率是多大?都有什么封装形式的?

答:有三种频率可以选择:300kH、600kHz、1.2MHz。封装只有一种,即LFCSP,CP-32-2。

问:ADP2114强制 PWM工作是如何降低EMI的?

答:ADP2114强制PWM工作时,将使芯片在整个负载范围内始终工作在同一个恒定频率,因此相比较 PFM/PWM自动模式(开关频率会在轻载时自动变化)来说,PWM工作能够降低系统EMI以及系统噪声。

问:FPGA电源的斜升时间(ramp-time)有哪些要求?

答:为确保供电,核心电压VCCINT校正时间必须在一定范围内。对于一些FPGA,过大的校正时间会产生更长时间的供电电流,由于在变压器启动treashold中VCCINT需要更长时间。开启校正时间长会引起热压力,如果电源向FPGA提供大电流。一些DC/DC变压器提供可调节软启动,允许通过一个外部电容器控制校正时间。校正时间取决于FPGA制造商,典型取值为50ms~100ms。

问:FPGA 供电电源的电压功耗如何估计?电源功耗取决于哪些因素?

答:可以根据公式:Pd=(Vin-Vout)(IL)+(VIn) (Iground),其中IL是负载电流,根据公式可以看出与输入、输出电压、负载电流、对地电流有关。

问:电路如何设计才能得到低纹波、低EMI、低噪声电源?

答:首先选择的电源应该是低纹波、低噪声的电源,其次就是布局布线要参考芯片资料给出的建议。

作者:ADI公司 来源:中电网 2010-3

ADP2114(图4)是一款功能多样的同步降压开关稳压器,可满足各种客户负载点要求。两个PWM通道既可以配置为分别提供2A和2A(或3A/1A)电流的两路独立输出,也可以配置为提供4A电流的单路交错式输出。ADP2114可提供高功效,开关频率最高可达2MHz。在轻负载时,该器件可以设置为脉冲跳跃模式工作,以便提高功效,或者设置为强制PWM模式工作,以便降低电磁干扰(EMI)。ADP2114还具有欠压闭锁(UVLO)、迟滞、软启动和电源正常输出指示等特性;保护特性有输出短路保护和热关断等。可以利用极小电阻和电容对输出电压、电流限制、开关频率、脉冲跳跃工作模式和软启动时间进行外部编程。

图3 电容阻抗随频率的变化曲线

图4 ADP2114同步降压开关稳压器

该器件可用于多个终端市场,例如通信基础设施、工业和仪器仪表、医疗保健以及高端消费电子市场。在这些终端市场的主要应用是分布式电源系统中的负载点稳压器。

虽然DC- DC稳压器的功效远高于LDO,但通常认为其噪声太高,无法在不显著降低其它参数性能的情况下,直接为高性能模数转换器供电。模数转换器的噪声至少有两个来源:通过电源纹波直接耦合至转换器中的噪声,以及磁耦合效益引起的噪声。

图5所示为一种实验室设置,针对采用低噪声LDO供电和采用开关稳压器ADP2114供电两种情况,比较一个16位、125MSPS模数转换器的性能。评估所用的AD9268可实现非常低的噪声,信噪比(SNR)为 78dB。DC-DC转换器贡献的额外噪声或杂散成分很容易反映在该模数转换器的输出频谱中,因此-152dBm/Hz的低本底噪声使它非常适合评估开关电源。

图5 开关电源供电测试

我们将ADP2114与低噪声LDO稳压器进行比较。高性能、16位、125MSPS AD转换器AD9268的评估结果表明:采用开关稳压器ADP2114供电与采用低噪声LDO稳压器供电相比,性能未受影响。

因此,ADP2114可以为用户提供可配置能力、多样化功能和灵活性,并且具有低噪声特性和高转换效率。同时能够满足各种客户负载点电源要求,性价比高,是 FPGA、ASIC、DSP和微处理器供电的理想选择。ADI公司提供网络工具可方便设计导入,同时提供评估板,有助于实现快速导入。

更多详细内容,敬请登陆中电网在线座谈网址:http://seminar.eccn.com

问答选编

问:印刷电路板中大电流供电,除加宽导电铜箔外,是否需要进一步采取镀锡等措施?

答:加镀锡一定程度上可以加大散热面积,但是效果不一定特别明显,最好还是加宽加厚导电铜箔。

问:在供电时,如果没考虑上电顺序,对整个系统的运行会有什么影响?

答:这个问题要针对系统的各个功能模块对上电的要求,如果系统中的某些电路对上电有严格的顺序,没有考虑到的话,很可能导致系统不工作。

问:电源纹波对FPGA性能有何影响?

答:工作时期的电源纹波要求、供电系统的压降、电源通路的等效阻抗设计等参数都是用户要特别留意的。建议在做大设计的时候一定要做电源完整性仿真,且要严格满足设计约束。

问:在IPTV系统中的FPGA供电电源有什么要求吗?

答:IPTV系统中FPGA的电源需求比较复杂,多达三种供电要求:内核电压、I/O电压和辅助电压。为了实现可靠的系统性,必须对这些排序,需要用电压管理芯片。

问:I/O 是否可以承受5V电压?

答:这个取决于I/O的供电电压。如果数字部分是5V供电,那么就可以。

问:ADP2118的输出电感和电容如何选择?它和负载电流、缓升时间有多大关系?

答:ADP2118为内部补偿器件,因此对输出电感电容有一定的限制,输出电容一般不能小于47uF,输出电感建议为0.8~3.3uH(针对频率设置为1.4MHz)、1.5~3.3uH(针对频率设置为700kHz)。输出电感电容的选择和负载电流、软启动时间并无太大关系。

问:ADP2114的PWM频率是多大?都有什么封装形式的?

答:有三种频率可以选择:300kH、600kHz、1.2MHz。封装只有一种,即LFCSP,CP-32-2。

问:ADP2114强制 PWM工作是如何降低EMI的?

答:ADP2114强制PWM工作时,将使芯片在整个负载范围内始终工作在同一个恒定频率,因此相比较 PFM/PWM自动模式(开关频率会在轻载时自动变化)来说,PWM工作能够降低系统EMI以及系统噪声。

问:FPGA电源的斜升时间(ramp-time)有哪些要求?

答:为确保供电,核心电压VCCINT校正时间必须在一定范围内。对于一些FPGA,过大的校正时间会产生更长时间的供电电流,由于在变压器启动treashold中VCCINT需要更长时间。开启校正时间长会引起热压力,如果电源向FPGA提供大电流。一些DC/DC变压器提供可调节软启动,允许通过一个外部电容器控制校正时间。校正时间取决于FPGA制造商,典型取值为50ms~100ms。

问:FPGA 供电电源的电压功耗如何估计?电源功耗取决于哪些因素?

答:可以根据公式:Pd=(Vin-Vout)(IL)+(VIn) (Iground),其中IL是负载电流,根据公式可以看出与输入、输出电压、负载电流、对地电流有关。

问:电路如何设计才能得到低纹波、低EMI、低噪声电源?

答:首先选择的电源应该是低纹波、低噪声的电源,其次就是布局布线要参考芯片资料给出的建议。

作者:ADI公司 来源:中电网 2010-3

FPGA 电源管理 电压 电流 LDO 电源模块 电路 电容 电感 开关电源 ADI PCB 电阻 PWM 电子 DSP 仿真 变压器 电容器 相关文章:

- 基于FPGA的片上系统的无线保密通信终端(02-16)

- 基于Virtex-5 FPGA设计Gbps无线通信基站(05-12)

- 基于FPGA的DVI/HDMI接口实现(05-13)

- 基于ARM的嵌入式系统中从串配置FPGA的实现(06-09)

- 采用EEPROM对大容量FPGA芯片数据实现串行加载(03-18)

- 赛灵思:可编程逻辑不仅已是大势所趋,而且势不可挡(07-24)