针对FPGA内缺陷成团的电路可靠性设计研究

时间:07-24

来源:互联网

点击:

提高冗余容错电路可靠性策略的定量分析

由于成团因子与冗余容错电路等效面积之间存在复杂非线性关系,无法为上述策略建立分析模型进行定量分析。但当FPGA内只有小于冗余容错电路面积的缺陷团,且成团因子与冗余容错电路等效面积成线性关系,或者可以用线性关系近似时,则可以建立相应的分析模型进行定量分析。

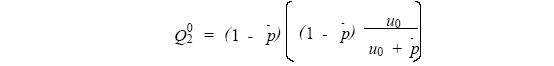

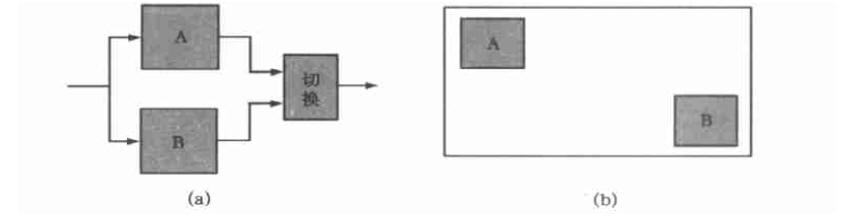

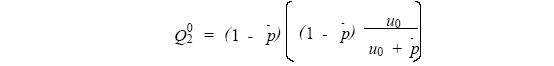

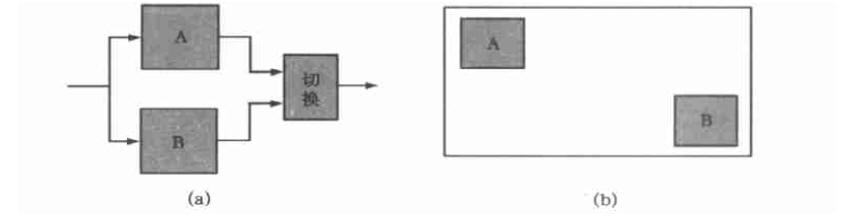

考虑一个单模块单备份容错电路,如图3 所示。A 是主份电路,B 是备份电路。如果单纯考虑信号时延,则布局时应将主、备份电路相邻排列。称这一布局为单模块单备份容错电路的基本布局,基本布局的等效面积为2S0(S0为主份电路面积) ,此时主、备份电路之间的距离为0,对应成团因子为u0,则有基本布局的失效概率Q02为

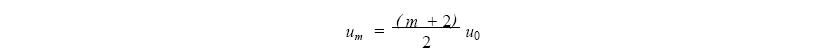

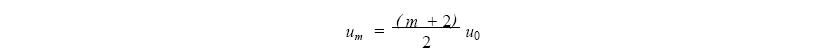

增大主、备份电路的距离,在主、备份之间留有面积等于m 个主份电路面积的空间。此布局为调整布局。调整布局的等效面积为(m+2)S0 ,此时主、备份电路之间的距离为m ,对应成团因子为um 。

um 和u0有如下关系

调整布局的失效率Qm

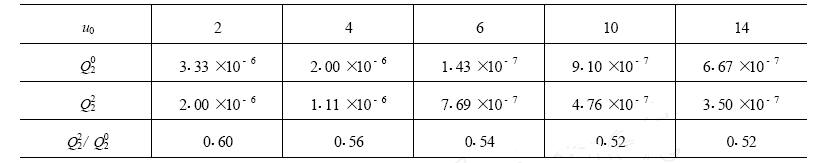

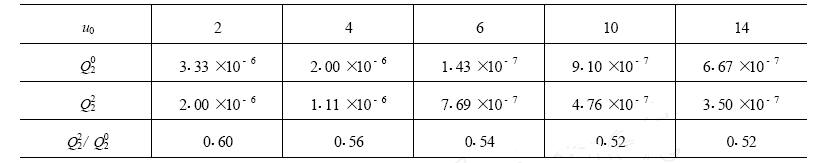

无论成团因子u0取何值,调整布局都能够降低冗余容错电路的失效率。表1 数据反映的是基本布局和特定调整布局(m=2)失效率随成团因子u0的变化情况,主份电路的可靠度p-=0.99999。

在成团因子较宽的一个变化范围内,特定调整布局(m=2)失效率比基本布局失效率降低了约1/2。

表1 失效率随成团因子u0 变化表

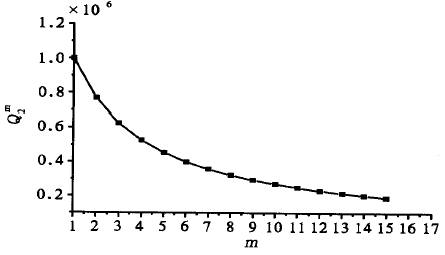

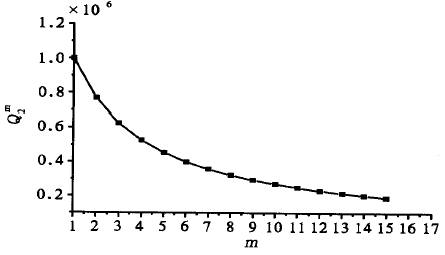

图4 冗余容错电路失效率随距离变化关系

冗余容错电路的主、备份电路间距离越大,冗余容错电路失效率越低。图4是冗余容错电路失效率随主、备份电路之间的距离变化(m变化)的情况,曲线对应的主份电路可靠度p-= 0.99999,成团因子u0=6。

表2 列出了不同布局失效率的具体改善数据,当m=8时,失效率约为基本布局的1/5。

表2 冗余容错电路失效率随布局变化表

缺陷成团时芯片内备份电路的优化布局原则

每种冗余容错方式,在FPGA的矩形(含正方形) 芯片内实现时,可以选择不同的布局方案。应用本章提出的策略,针对常用的几种冗余容错方式,从可靠性角度提出了最佳的一个布局方案。

图5(a)是单模块单备份容错形式。按图5(b)所示,将主、备份电路沿芯片对角线布置,可以获得最低的失效率。切换电路布置在与主、备份电路距离相同的位置上,保证切换电路的两路输入信号时延基本相同。主、备份电路的输入分别从就近的芯片引脚输入,避免占用内部大量的互连资源。两引脚再通过PCB板上的印制线相连。

图5 单模块单备份容错形式布局

布局、时延与资源利用率

依据本章提出的策略进行布局,冗余容错模块之间存在较大的空间,在这空间里可以布置其他功能电路。但是冗余容错模块之间的长距离信号连接需要消耗FPGA内有限的连线资源,往往由于连线资源消耗殆尽,无法继续布置其他的功能电路,从而降低了芯片逻辑资源的利用率。因此,冗余容错模块可靠性的提升也是以牺牲资源为代价的。解决这一问题的一个有效办法是利用FPGA丰富的输入输出管脚资源,将片内的长线连接改为片外PCB板印制导线的连接。

无论是片内的还是片外的长线连接,都势必引起较大的信号时延,这会限制电路的最高工作频率,但随着FPGA性能的不断改善,信号时延问题会逐步缓解。

结束语

基本FPGA的片内冗余容错将会是提高微小卫星可靠性的重要手段。随着FPGA规模的增大和集成密度的提高,内部缺陷发生的概率也在增大,因此研究缺陷成团性对片内冗余容错的影响,具有较重要的工程价值。后续工作需要研究缺陷成团对一些常用片内冗余容错方式如TMR的影响,提出相应的应对策略。在此基础上再进一步探讨在电子设计自动化环境下,高效实现应对缺陷成团性策略的方法。

由于成团因子与冗余容错电路等效面积之间存在复杂非线性关系,无法为上述策略建立分析模型进行定量分析。但当FPGA内只有小于冗余容错电路面积的缺陷团,且成团因子与冗余容错电路等效面积成线性关系,或者可以用线性关系近似时,则可以建立相应的分析模型进行定量分析。

考虑一个单模块单备份容错电路,如图3 所示。A 是主份电路,B 是备份电路。如果单纯考虑信号时延,则布局时应将主、备份电路相邻排列。称这一布局为单模块单备份容错电路的基本布局,基本布局的等效面积为2S0(S0为主份电路面积) ,此时主、备份电路之间的距离为0,对应成团因子为u0,则有基本布局的失效概率Q02为

增大主、备份电路的距离,在主、备份之间留有面积等于m 个主份电路面积的空间。此布局为调整布局。调整布局的等效面积为(m+2)S0 ,此时主、备份电路之间的距离为m ,对应成团因子为um 。

um 和u0有如下关系

调整布局的失效率Qm

无论成团因子u0取何值,调整布局都能够降低冗余容错电路的失效率。表1 数据反映的是基本布局和特定调整布局(m=2)失效率随成团因子u0的变化情况,主份电路的可靠度p-=0.99999。

在成团因子较宽的一个变化范围内,特定调整布局(m=2)失效率比基本布局失效率降低了约1/2。

表1 失效率随成团因子u0 变化表

图4 冗余容错电路失效率随距离变化关系

冗余容错电路的主、备份电路间距离越大,冗余容错电路失效率越低。图4是冗余容错电路失效率随主、备份电路之间的距离变化(m变化)的情况,曲线对应的主份电路可靠度p-= 0.99999,成团因子u0=6。

表2 列出了不同布局失效率的具体改善数据,当m=8时,失效率约为基本布局的1/5。

表2 冗余容错电路失效率随布局变化表

缺陷成团时芯片内备份电路的优化布局原则

每种冗余容错方式,在FPGA的矩形(含正方形) 芯片内实现时,可以选择不同的布局方案。应用本章提出的策略,针对常用的几种冗余容错方式,从可靠性角度提出了最佳的一个布局方案。

图5(a)是单模块单备份容错形式。按图5(b)所示,将主、备份电路沿芯片对角线布置,可以获得最低的失效率。切换电路布置在与主、备份电路距离相同的位置上,保证切换电路的两路输入信号时延基本相同。主、备份电路的输入分别从就近的芯片引脚输入,避免占用内部大量的互连资源。两引脚再通过PCB板上的印制线相连。

图5 单模块单备份容错形式布局

布局、时延与资源利用率

依据本章提出的策略进行布局,冗余容错模块之间存在较大的空间,在这空间里可以布置其他功能电路。但是冗余容错模块之间的长距离信号连接需要消耗FPGA内有限的连线资源,往往由于连线资源消耗殆尽,无法继续布置其他的功能电路,从而降低了芯片逻辑资源的利用率。因此,冗余容错模块可靠性的提升也是以牺牲资源为代价的。解决这一问题的一个有效办法是利用FPGA丰富的输入输出管脚资源,将片内的长线连接改为片外PCB板印制导线的连接。

无论是片内的还是片外的长线连接,都势必引起较大的信号时延,这会限制电路的最高工作频率,但随着FPGA性能的不断改善,信号时延问题会逐步缓解。

结束语

基本FPGA的片内冗余容错将会是提高微小卫星可靠性的重要手段。随着FPGA规模的增大和集成密度的提高,内部缺陷发生的概率也在增大,因此研究缺陷成团性对片内冗余容错的影响,具有较重要的工程价值。后续工作需要研究缺陷成团对一些常用片内冗余容错方式如TMR的影响,提出相应的应对策略。在此基础上再进一步探讨在电子设计自动化环境下,高效实现应对缺陷成团性策略的方法。

集成电路 FPGA 电路 电子 CPLD PCB 自动化 相关文章:

- 周立功:如何兼顾学习ARM与FPGA(05-23)

- 初学者如何学习FPGA(08-06)

- 为何、如何学习FPGA(05-23)

- FPGA 重复配置和测试的实现(08-14)

- 适用于消费性市场的nano FPGA技术(09-27)

- 赛灵思“授之以渔”理论:危机中如何巧降成本(06-04)