基于单片机的CPLD/FPGA被动串行下载配置的实现

时间:07-22

来源:互联网

点击:

1引言

随着电子技术的发展,当前数字系统的设计正朝着速度快、容量大、体积小、重量轻的方向发展。推动该潮流迅猛发展的引擎就是日趋进步和完善的高密度现场可编程逻辑器件设计技术。高密度现场可编程逻辑器件(CPLD/FPGA)能够将大量逻辑功能集成于一个单片IC之中,对基于E2PROM(或FlashMemory)工艺的器件,配置数据在掉电后不会丢失,可以直接采用ByteBlaster并口下载电缆对他们进行配置,但基于该架构的器件的集成度较低,一般在10万门以下;然而对基于SRAM工艺的器件,配置数据在器件掉电后会丢失,但基于该架构的器件的集成度相对较高,一般在1万门以上。

由于当前项目开发中所需使用的可编程逻辑器件的集成度要求越来越高,基于SRAM工艺的器件得到越来越广泛的使用,那么此时如何将配置数据成功地写入目标器件,并且保证其在掉电再上电后能够自动恢复配置数据,成为电子设计工程师能否正确使用基于SRAM工艺的器件必须掌握的一项技术。

针对基于SRAM工艺的器件的下载配置问题,本文介绍采用AT89S2051单片机配合串行E2PROM存储器,实现CPLD/FPGA器件的被动串行(PS)模式的下载配置。

2 系统组成

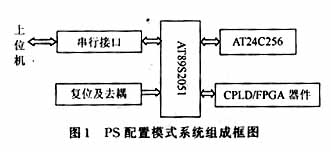

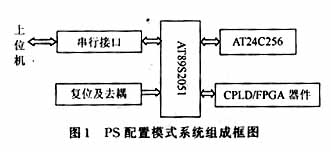

该系统的硬件电路由AT89S2051单片机、AT24C256串行E2PROM,MAX232串行接口电路、复位及去耦合电路和被配置CPLD/FPGA器件组成,如图1所示。

3 系统硬件设计

3.1 芯片选型

(1)单片机单片机采用ATMEL公司生产的AT89S2051单片机,该芯片与MCS51系列单片机兼容。内含:2kBFlashE2PROM,128BRAM,15根I/O引线,2个16位定时器/计数器,1个5向量两级中断结构,1个全双工串行口和1个精密模拟电压比较器等。

(2)串行E2PROM由于基于SRAM工艺的可编程逻辑器件(CPLD/FPGA)的配置数据在掉电后会丢失,需要外加存储器以保存配置数据。为了尽量减小电路板的面积,选用8脚的串行E?2PROMAT24C256。AT24C256是ATMEL公司生产的2线制串行电可擦写只读存储器,具有自定时写周期特性,容量32kB。该器件特别适合于对功耗有严格要求的应用场合。

(3)通信接口采用MAXIM公司生产的串行接口芯片MAX232将PC机与下载配置电路连接起来。下载配置电路通过该串口接收PC机下传的命令,执行相应的操作再将处理结果上传到PC机。MAX232是通用+5V供电的多通道RS232总线收发器,尤其适合在电池供电的系统中应用。

3.2 硬件原理图

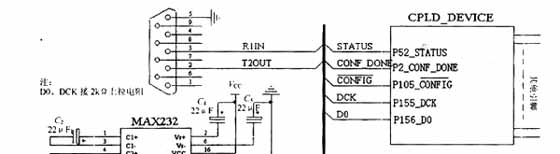

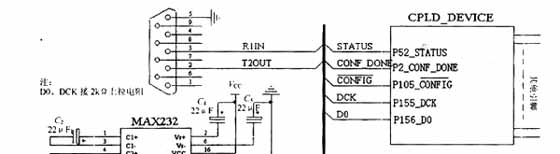

硬件原理如图2所示。上电后,单片机首先调用子程序完成如下操作:将掉电前已经存储在AT24C256串行E2PROM中的器件配置文件读出;采用被动串行模式(PS)将该文件配置到CPLD/FPGA器件中,从而实现器件掉电再上电后自动恢复配置数据的功能。然后,单片机就会工作在动态停机状态,在此过程中,单片机可以响应串口中断。

如果单片机响应串口中断并且接收到一个数据,那么单片机首先判断该数据所表示的命令类型,若是配置命令,单片机就进入配置状态。在配置状态下,单片机一边接收配置数据,一边将这些数据写到CPLD/FPGA器件中;若是写E2PROM命令,单片机就进入写E2PROM状态,此时单片机会一边接收配置数据,一边将这些数据写到配置用E2PROM中(注意此时这些数据并没有被配置到CPLD/FPGA器件中);若是读E2PROM命令,单片机就进入读E2PROM并配置CPLD/FPGA器件状态,此时单片机会一边读E2PROM中的配置数据,一边将读出的配置数据写到CPLD/FPGA器件中。

4 系统软件设计

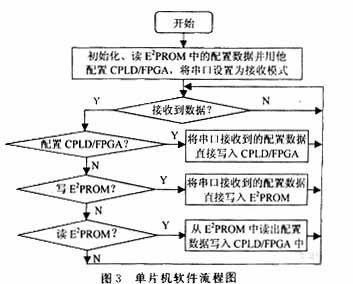

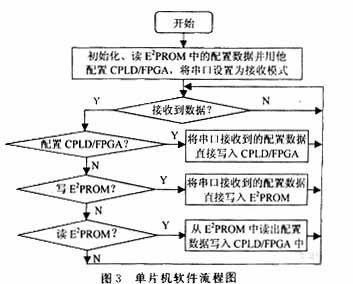

软件包括:主程序、下载配置子程序、写E2PROM子程序、读E2PROM子程序及通用延时子程序构成。其软件流程图如图3所示。

现将以上所提及的各个子程序的用途简介如下:

下载配置子程序的作用是将从串口接收的配置数据直接写到目标器件中,即直接写到可编程逻辑器件(CPLD/FPGA)中。

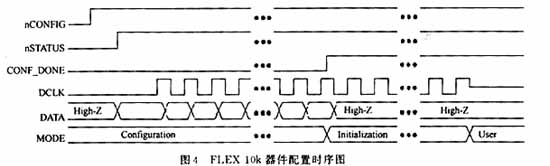

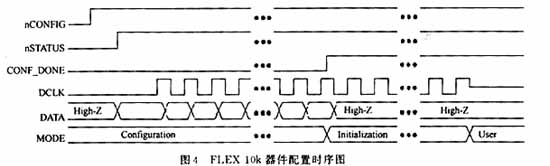

在编写该子程序时,必须注意目标器件的写入时序。必须根据目标器件生产厂家提供的时序图,用单片机语言编程将其配置时序准确地描述出来,只有这样才能正确地将配置数据写入到目标器件中。例如,我们若要正确配置ALTERA公司生产的FLEX10k系列器件,就必须严格遵守以下时序图,如图4所示。

写E2PROM子程序的作用是将从串口接收的配置数据直接写到AT24C256串行E2PROM中保存起来,以备需要时可以用这些保存的数据重新配置器件。读E2PROM子程序的作用是从AT24C256中将配置数据读出,同时将这些配置数据写到目标器件中,以实现对目标器件的重新配置。

在编写这两个子程序时,必须注意AT24C256的数据写入和数据读出时序,只有严格遵守该时序图,才能正确地对该存储器进行读写操作。其读写时序如图5所示。

通用延时子程序可以灵活地设定延时时间间隔。当程序中需要延时的时候只要先给该子程序提供一个延时时间常数,再调用延时子程序即可。例如,通常在系统复位时为了让处理器复位后系统中其他器件能可靠复位而调用的上电延时子程序就可以采用该通用延时子程序来实现。

5 结语

本系统可用于配置所有ALTERA公司生产的基于SRAM架构的CPLD器件和XILINX公司生产的基于SRAM架构的FPGA器件以及其他主流器件制造公司生产的基于SRAM架构的器件,具有很强的通用性。由于该电路使用的元器件非常少,也可以将其制作成面积很小、便于携带的通用下载配置板使用。该下载配置电路经本人实际制作、调试、使用,其工作稳定可靠,具有很好的应用前景。

随着电子技术的发展,当前数字系统的设计正朝着速度快、容量大、体积小、重量轻的方向发展。推动该潮流迅猛发展的引擎就是日趋进步和完善的高密度现场可编程逻辑器件设计技术。高密度现场可编程逻辑器件(CPLD/FPGA)能够将大量逻辑功能集成于一个单片IC之中,对基于E2PROM(或FlashMemory)工艺的器件,配置数据在掉电后不会丢失,可以直接采用ByteBlaster并口下载电缆对他们进行配置,但基于该架构的器件的集成度较低,一般在10万门以下;然而对基于SRAM工艺的器件,配置数据在器件掉电后会丢失,但基于该架构的器件的集成度相对较高,一般在1万门以上。

由于当前项目开发中所需使用的可编程逻辑器件的集成度要求越来越高,基于SRAM工艺的器件得到越来越广泛的使用,那么此时如何将配置数据成功地写入目标器件,并且保证其在掉电再上电后能够自动恢复配置数据,成为电子设计工程师能否正确使用基于SRAM工艺的器件必须掌握的一项技术。

针对基于SRAM工艺的器件的下载配置问题,本文介绍采用AT89S2051单片机配合串行E2PROM存储器,实现CPLD/FPGA器件的被动串行(PS)模式的下载配置。

2 系统组成

该系统的硬件电路由AT89S2051单片机、AT24C256串行E2PROM,MAX232串行接口电路、复位及去耦合电路和被配置CPLD/FPGA器件组成,如图1所示。

3 系统硬件设计

3.1 芯片选型

(1)单片机单片机采用ATMEL公司生产的AT89S2051单片机,该芯片与MCS51系列单片机兼容。内含:2kBFlashE2PROM,128BRAM,15根I/O引线,2个16位定时器/计数器,1个5向量两级中断结构,1个全双工串行口和1个精密模拟电压比较器等。

(2)串行E2PROM由于基于SRAM工艺的可编程逻辑器件(CPLD/FPGA)的配置数据在掉电后会丢失,需要外加存储器以保存配置数据。为了尽量减小电路板的面积,选用8脚的串行E?2PROMAT24C256。AT24C256是ATMEL公司生产的2线制串行电可擦写只读存储器,具有自定时写周期特性,容量32kB。该器件特别适合于对功耗有严格要求的应用场合。

(3)通信接口采用MAXIM公司生产的串行接口芯片MAX232将PC机与下载配置电路连接起来。下载配置电路通过该串口接收PC机下传的命令,执行相应的操作再将处理结果上传到PC机。MAX232是通用+5V供电的多通道RS232总线收发器,尤其适合在电池供电的系统中应用。

3.2 硬件原理图

硬件原理如图2所示。上电后,单片机首先调用子程序完成如下操作:将掉电前已经存储在AT24C256串行E2PROM中的器件配置文件读出;采用被动串行模式(PS)将该文件配置到CPLD/FPGA器件中,从而实现器件掉电再上电后自动恢复配置数据的功能。然后,单片机就会工作在动态停机状态,在此过程中,单片机可以响应串口中断。

如果单片机响应串口中断并且接收到一个数据,那么单片机首先判断该数据所表示的命令类型,若是配置命令,单片机就进入配置状态。在配置状态下,单片机一边接收配置数据,一边将这些数据写到CPLD/FPGA器件中;若是写E2PROM命令,单片机就进入写E2PROM状态,此时单片机会一边接收配置数据,一边将这些数据写到配置用E2PROM中(注意此时这些数据并没有被配置到CPLD/FPGA器件中);若是读E2PROM命令,单片机就进入读E2PROM并配置CPLD/FPGA器件状态,此时单片机会一边读E2PROM中的配置数据,一边将读出的配置数据写到CPLD/FPGA器件中。

4 系统软件设计

软件包括:主程序、下载配置子程序、写E2PROM子程序、读E2PROM子程序及通用延时子程序构成。其软件流程图如图3所示。

现将以上所提及的各个子程序的用途简介如下:

下载配置子程序的作用是将从串口接收的配置数据直接写到目标器件中,即直接写到可编程逻辑器件(CPLD/FPGA)中。

在编写该子程序时,必须注意目标器件的写入时序。必须根据目标器件生产厂家提供的时序图,用单片机语言编程将其配置时序准确地描述出来,只有这样才能正确地将配置数据写入到目标器件中。例如,我们若要正确配置ALTERA公司生产的FLEX10k系列器件,就必须严格遵守以下时序图,如图4所示。

写E2PROM子程序的作用是将从串口接收的配置数据直接写到AT24C256串行E2PROM中保存起来,以备需要时可以用这些保存的数据重新配置器件。读E2PROM子程序的作用是从AT24C256中将配置数据读出,同时将这些配置数据写到目标器件中,以实现对目标器件的重新配置。

在编写这两个子程序时,必须注意AT24C256的数据写入和数据读出时序,只有严格遵守该时序图,才能正确地对该存储器进行读写操作。其读写时序如图5所示。

通用延时子程序可以灵活地设定延时时间间隔。当程序中需要延时的时候只要先给该子程序提供一个延时时间常数,再调用延时子程序即可。例如,通常在系统复位时为了让处理器复位后系统中其他器件能可靠复位而调用的上电延时子程序就可以采用该通用延时子程序来实现。

5 结语

本系统可用于配置所有ALTERA公司生产的基于SRAM架构的CPLD器件和XILINX公司生产的基于SRAM架构的FPGA器件以及其他主流器件制造公司生产的基于SRAM架构的器件,具有很强的通用性。由于该电路使用的元器件非常少,也可以将其制作成面积很小、便于携带的通用下载配置板使用。该下载配置电路经本人实际制作、调试、使用,其工作稳定可靠,具有很好的应用前景。

电子 CPLD FPGA 单片机 电路 51单片机 电压 比较器 总线 收发器 LTE 相关文章:

- 基于ARM的嵌入式系统中从串配置FPGA的实现(06-09)

- 周立功:如何兼顾学习ARM与FPGA(05-23)

- 初学者如何学习FPGA(08-06)

- 为何、如何学习FPGA(05-23)

- 学习FPGA绝佳网站推荐!!!(05-23)

- 我的FPGA学习历程(05-23)