高速上下变频FIR滤波器的FPGA设计

时间:07-24

来源:互联网

点击:

滤波器是通信系统中的重要部件。数字滤波器的实现一般有3 条途径: (1) 由通用DSP 芯片编程实现; (2) 选用已有的专用滤波器芯片实现; (3) 根据系统要求自行设计滤波器, 并用FPGA 实现。随着数字通信速率的快速提高, 对滤波器的运算速度的要求也愈来愈高。在数据传输率为54M b it?s, 符合HyperL an2 的宽带无线WLAN 收发器的研究实验中, 数据的基带速率为20MByte?s, 经4 倍升采样为80MByte?s, 在此升采样(在接收链路中为降采样) 过程中必须实现数字上下变频和抗混叠滤波器。如此高速的滤波器如用通用DSP 实现, 则将占用该DSP 的绝大部分运算资源, 使DSP 几乎不能承担其他编解码等任务。

这种情况下, 最好的选择是用FPGA 硬件实现上下变频和滤波。虽然目前市场上有一些用于FPGA 实现上下变频和F IR滤波器的IP 软核, 但这些软核由于追求通用性和可配置性, 在代码效率、运行速度、系统集成紧凑性和FPGA 资源用量最小化等方面很难满足要求或达到最优化。

因此, 根据具体系统的运行要求, 暂不强求通用性和可重新配置性, 而着重研究实现上下变频滤波的高速度和FPGA 资源用量最小化。资源用量最小化可以在一片FPGA 上集成更多的功能电路, 例如增益自动控制功能等, 即可能实现片上系统(SoC)。为了在实现高速的同时, 减少FP2GA 的资源占用量, 一方面可以研究具体FPGA 的底层结构特点, 人工干预底层电路综合来组建系统, 另一方面要研究被设计电路的实现结构、算法和编码方式等, 从中选择快速有效和硬件复杂度最低的实现方法。

本文根据宽带WLAN 的收发器要求, 在系统总体结构安排、滤波器结构设计、乘加运算算法, 以及流水线实现等方面进行研究, 在实现高速度的同时, 使得系统资源的占用量达到最小。

达到这一目标的主要技术要点有: (1) 充分利用上下变频器结构特点, 只用一套滤波器运算单元实现上变频滤波和下变频滤波; (2) 充分利用收发器的数据流特点和F IR 滤波器系数特点, 用该滤波器运算单元同时实现对I,Q 两个数据流的变频和滤波; (3) 分别用传统滤波器的转置结构和独特的位平面结构设计实现高速上下变频和滤波(80MHz 运算速度的40 阶上下变频F IR 滤波器)。并对二者的实现结构和综合结果进行比较, 说明在达到同样速度的前提下, 位平面结构仅占用转置结构所用逻辑资源的一半。在下一步对位平面结构的通用性设计有所改进后, 位平面结构应成为高速滤波器的主要设计方法; (4) 合理划分和优化各级流水线的性能是实现上下变频滤波高速运行的关键。

宽带无线通信的数字上下变频

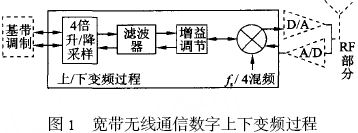

数字上下变频过程是数字通信系统中必不可少的实现环节。上变频就是用数字信号处理的手段将基带已调制信号的频带搬移到中频( IF) 的过程。上变频得到的数字IF 信号经DAC 变换为模拟信号后, 再在模拟域变换为RF 信号, 通过天线发送出去, 实现数字信号的发送(图1 的右箭头方向表示信号的发送步骤)。无线信号的接收过程(图1 的左箭头方向) 和发送过程完全相反, 即在A?D 变换得到数字IF 后, 经数字下变频变换为基带调制信号, 再经数字解调最后得到接收的信息。在符合HyperLan2 传输协议的WLAN 的收发器实验中,数据传输率高达54M b it?s, 其基带O FDM 调制输出的I,Q 信号采样频率高达20MBytes。

图1 实线框内是本文设计实现的上下变频过程, 它们被集成在一片FPGA 上。基带输出的I,Q 信号, 经4 倍增采样、去混叠滤波、增益补偿后和20MHz (f s?4混频, f s 为采样频率) 的数字载波信号复混频。数字IF 信号的采样率升为80M SPS, 基带信号的中心频率被移至20MHz。这一过程中滤波器起着至关重要的作用, 它保证基带信号的频谱在升降采样过程和混频过程中不发生混叠和展宽。滤波器的主要指标为: Remez 40 阶低通F IR 滤波器; 通带带宽10MHz; 阻带抑制比- 50 dB; 输入信号采样频率80MHz; 滤波器系数量化为12bit 有符号数表示。

上下变频滤波器的实现

滤波器的输入数据流特点

基带调制的信号输出形式是I (8bit) 和Q (8bit ) 的并行输出. 在数据发送方式时, I,Q 信号直接馈入上变频器。4 倍升采样过程是分别在I 和Q序列中每相邻点之间插入3 个0, 从而数据率升为80MHz。利用升采样后的这一特点, 可以将并行的I,Q 数据串行化, 如图2 (a) 所示。在接收数据方式下, RF 信号经80MSPS 的AD 采样后输出馈入下变频器。在下变频器中的第一步处理是中心频率下移的复混频。输入信号分别和相位相差90°的正弦波数字相乘, 从而分解出I,Q 两路信号。用于复混频的正弦波和余弦波的中心频率为20MHz, 每周期取4 个点, 其中有2 个点为0, 另2 个点分别为+ 1 和- 1。这样得到的I,Q 信号相邻两点之间必为零值, 如图2 (b) 所示。和发送工作方式一样, 可以将并行的I,Q 信号串行化。这样在两种工作方式下, 滤波器的输入并行数据流均先变换成8bit宽的串行输入流。

这种情况下, 最好的选择是用FPGA 硬件实现上下变频和滤波。虽然目前市场上有一些用于FPGA 实现上下变频和F IR滤波器的IP 软核, 但这些软核由于追求通用性和可配置性, 在代码效率、运行速度、系统集成紧凑性和FPGA 资源用量最小化等方面很难满足要求或达到最优化。

因此, 根据具体系统的运行要求, 暂不强求通用性和可重新配置性, 而着重研究实现上下变频滤波的高速度和FPGA 资源用量最小化。资源用量最小化可以在一片FPGA 上集成更多的功能电路, 例如增益自动控制功能等, 即可能实现片上系统(SoC)。为了在实现高速的同时, 减少FP2GA 的资源占用量, 一方面可以研究具体FPGA 的底层结构特点, 人工干预底层电路综合来组建系统, 另一方面要研究被设计电路的实现结构、算法和编码方式等, 从中选择快速有效和硬件复杂度最低的实现方法。

本文根据宽带WLAN 的收发器要求, 在系统总体结构安排、滤波器结构设计、乘加运算算法, 以及流水线实现等方面进行研究, 在实现高速度的同时, 使得系统资源的占用量达到最小。

达到这一目标的主要技术要点有: (1) 充分利用上下变频器结构特点, 只用一套滤波器运算单元实现上变频滤波和下变频滤波; (2) 充分利用收发器的数据流特点和F IR 滤波器系数特点, 用该滤波器运算单元同时实现对I,Q 两个数据流的变频和滤波; (3) 分别用传统滤波器的转置结构和独特的位平面结构设计实现高速上下变频和滤波(80MHz 运算速度的40 阶上下变频F IR 滤波器)。并对二者的实现结构和综合结果进行比较, 说明在达到同样速度的前提下, 位平面结构仅占用转置结构所用逻辑资源的一半。在下一步对位平面结构的通用性设计有所改进后, 位平面结构应成为高速滤波器的主要设计方法; (4) 合理划分和优化各级流水线的性能是实现上下变频滤波高速运行的关键。

宽带无线通信的数字上下变频

数字上下变频过程是数字通信系统中必不可少的实现环节。上变频就是用数字信号处理的手段将基带已调制信号的频带搬移到中频( IF) 的过程。上变频得到的数字IF 信号经DAC 变换为模拟信号后, 再在模拟域变换为RF 信号, 通过天线发送出去, 实现数字信号的发送(图1 的右箭头方向表示信号的发送步骤)。无线信号的接收过程(图1 的左箭头方向) 和发送过程完全相反, 即在A?D 变换得到数字IF 后, 经数字下变频变换为基带调制信号, 再经数字解调最后得到接收的信息。在符合HyperLan2 传输协议的WLAN 的收发器实验中,数据传输率高达54M b it?s, 其基带O FDM 调制输出的I,Q 信号采样频率高达20MBytes。

图1 实线框内是本文设计实现的上下变频过程, 它们被集成在一片FPGA 上。基带输出的I,Q 信号, 经4 倍增采样、去混叠滤波、增益补偿后和20MHz (f s?4混频, f s 为采样频率) 的数字载波信号复混频。数字IF 信号的采样率升为80M SPS, 基带信号的中心频率被移至20MHz。这一过程中滤波器起着至关重要的作用, 它保证基带信号的频谱在升降采样过程和混频过程中不发生混叠和展宽。滤波器的主要指标为: Remez 40 阶低通F IR 滤波器; 通带带宽10MHz; 阻带抑制比- 50 dB; 输入信号采样频率80MHz; 滤波器系数量化为12bit 有符号数表示。

上下变频滤波器的实现

滤波器的输入数据流特点

基带调制的信号输出形式是I (8bit) 和Q (8bit ) 的并行输出. 在数据发送方式时, I,Q 信号直接馈入上变频器。4 倍升采样过程是分别在I 和Q序列中每相邻点之间插入3 个0, 从而数据率升为80MHz。利用升采样后的这一特点, 可以将并行的I,Q 数据串行化, 如图2 (a) 所示。在接收数据方式下, RF 信号经80MSPS 的AD 采样后输出馈入下变频器。在下变频器中的第一步处理是中心频率下移的复混频。输入信号分别和相位相差90°的正弦波数字相乘, 从而分解出I,Q 两路信号。用于复混频的正弦波和余弦波的中心频率为20MHz, 每周期取4 个点, 其中有2 个点为0, 另2 个点分别为+ 1 和- 1。这样得到的I,Q 信号相邻两点之间必为零值, 如图2 (b) 所示。和发送工作方式一样, 可以将并行的I,Q 信号串行化。这样在两种工作方式下, 滤波器的输入并行数据流均先变换成8bit宽的串行输入流。

滤波器 DSP FPGA 收发器 电路 SoC DAC Xilinx VHDL 仿真 相关文章:

- 数字下变频的FPGA实现(05-12)

- 用FPGA实现音频采样率的转换(02-07)

- 基于FPGA的任意时延伪码序列产生方法(04-12)

- 基于FPGA实现变采样率FIR滤波器的研究(04-13)

- 基于CPLD的CCD信号发生器的研究(04-08)

- 利用FPGA和CPLD数字逻辑实现ADC(06-04)