针对FPGA内缺陷成团的电路可靠性设计研究

时间:07-24

来源:互联网

点击:

缺陷成团对FPGA片内冗余容错电路可靠性的影响

卫星电子系统的功能电路布局于FPGA内,功能电路由芯片内的若干简单逻辑块构成。为提高功能电路的可靠性,往往需要在片内对功能电路整体采取冗余容错措施,如最常用的单备份冗余容错形式。冗余容错电路包括主份电路、若干备份电路和切换电路,其可靠性是由主份电路、备份电路和切换电路共同决定的。如果主份和备份电路远比切换电路复杂,则可以忽略切换电路对冗余容错电路可靠性的影响,以下的讨论就是针对这一情况进行的。

对于冗余容错电路,不允许主份和备份电路都出现故障,引起冗余容错电路失效。因此有必要采取措施,尽可能降低冗余容错电路的失效率。

无论是FPGA内逻辑单元一类的简单逻辑块,还是处理器阵列中的处理器单元(PE)一类的复杂逻辑块,都可以采用成品率复合二项式分布模型分析其成品率。若把冗余容错电路的主份和备份电路分别看成是片内的一个复杂逻辑块,则可以用此模型分析缺陷成团对冗余容错电路可靠性产生的影响。

复合二项式分布模型的数学推导

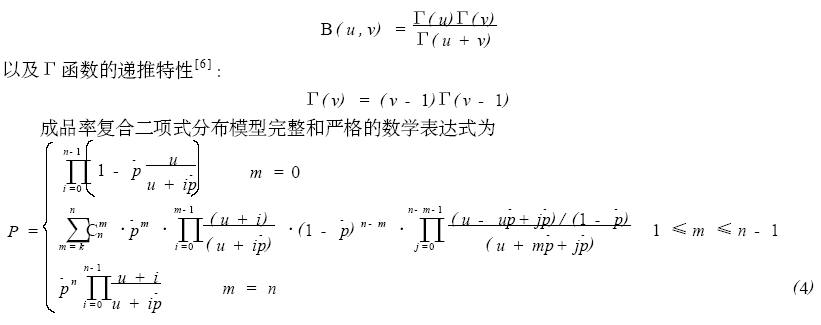

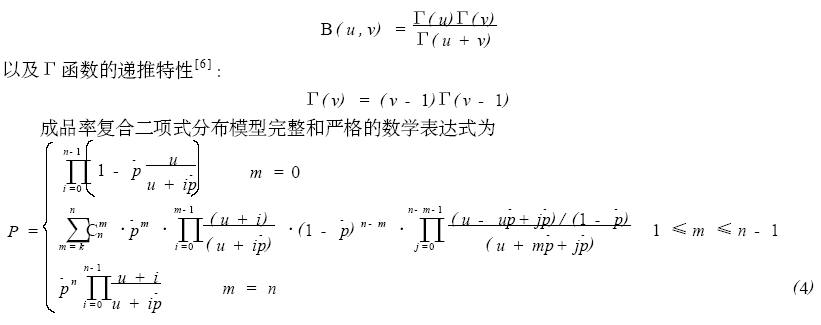

经分析,式(3)给出的成品率复合二项式分布模型表达式存在错误,Stapper在文献中没有给出推导过程,因此首先从数学上对此模型进行了严格推导。推导的关键是利用Γ函数与B函数的关系:

缺陷成团对冗余容错电路可靠性影响分析

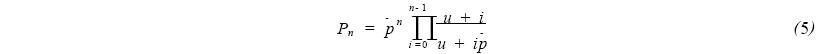

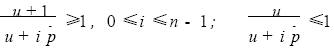

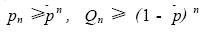

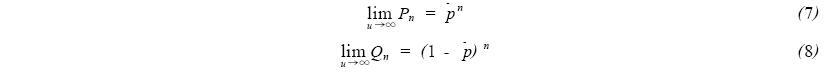

式(4)中的第三项对应n冗余容错电路的无故障概率Pn为

式(4) 中的第一项对应n 冗余容错电路的失效率Qn 为

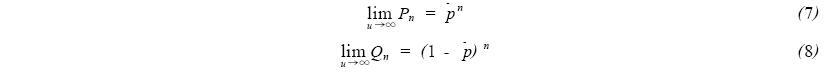

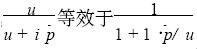

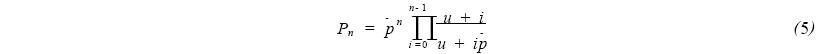

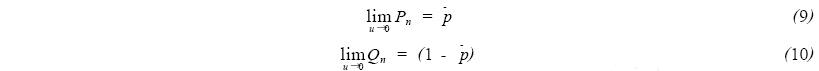

分析式(5) 、(6) ,当参数u 趋近于无穷大时

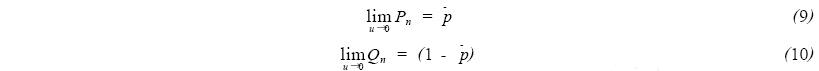

当参数u 趋近于零时

式(7)、(8)表明,当参数u 趋近于无穷大时,Pn和Qn的值等于缺陷均匀分布时的值,说明此时缺陷不具备成团性,而是呈均匀分布状态; 式(9)、(10)表明,当参数u趋近于零时,Pn和Qn的值分别等于主份电路的可靠度和共效率。

参数u反映了IC 内部缺陷成团性的强弱,称为模型的成团因子。u 越大,缺陷成团性越弱;u 越小,缺陷成团性越强。

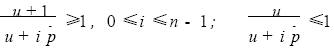

进一步分析表达式(5)、(6),对于任意的u>0 ,由于

所以有

。

缺陷成团时片内冗余容错电路的无故障概率和失效率比缺陷均匀分布时的都要高。缺陷成团性增大了冗余容错电路的失效率,削弱了冗余容错的可靠性增长功效。

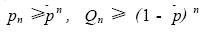

多项式

,其值随参数u增大而增大,因此失效率Qn随参数u增大而减小,并且在u=0时取得最大值。成团因子u越大,冗余容错电路的失效率越低、可靠性就越高。这一结论对冗余容错电路可靠性设计具有重要指导意义。

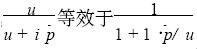

成团因子

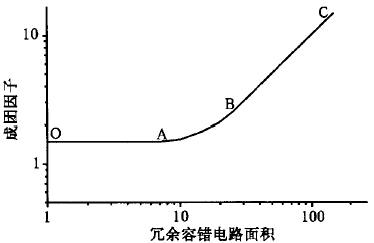

缺陷成团性强弱可以理解为缺陷相关性的强弱。缺陷成团性越强,缺陷相关性就越强,成团因子越小,反之亦然。若应用式(4)分析一个冗余容错电路,则成团因子反映的是冗余容错电。路内缺陷的平均相关度缺陷团面积是个随机值,当冗余容错电路面积小于最小缺陷团面积时,相应成团因子的值只取决于缺陷团内缺陷相关性的强弱,与冗余容错电路面积无关;当冗余容错电路面积大于最大缺陷团面积时,此时成团因子不仅受缺陷成团性强弱的影响,而且随冗余容错电路面积的变化而变化。

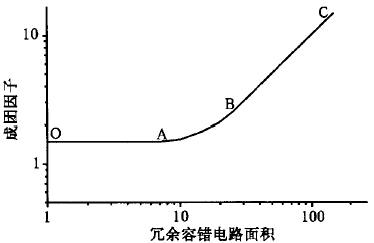

图2 成团因子α与冗余容错电路面积的关系

IC成品率预计常用到负二项式分布模型,此模型中的参数α是模型的成团因子。Stapper采用回归分析法分析验证成团因子α,得出成团因子与冗余容错电路面积的关系,如图2所示。曲线中的OA水平直线段表示α维持不变,对应冗余容错电路面积小于所有缺陷团面积的情况;曲线中的BC直线段表明α与冗余容错电路块面积成正比,对应冗余容错电路面积大于所有缺陷团面积的情况; 曲线中的AB曲线段表明α随冗余容错电路面积增大而呈现非线性增长,此时冗余容错电路面积介于最小缺陷团面积和最大缺陷团面积之间。

在没有缺陷团面积数据时,一般假定FPGA内缺陷团面积小至逻辑块,大至整个芯片,并且在这范围内连续分布。此时图2中的点A、B分别趋近点O、C,在曲线整个范围内,成团因子随冗余容错电路块面积增大而呈非线性增长。

实验数据表明,在冗余容错电路面积小于所有缺陷团面积时,成团成子u维持不变。成团因子α和u物理意义相同,遵循相似的变化规律。

缺陷成团时提高冗余容错电路可靠性的策略

冗余容错电路的主份和备份电路布局于FPGA芯片内。当FPGA内缺陷成团时,可以通过调整布局,增大主、备份电路的几何距离,降低冗余容错电路的失效率。

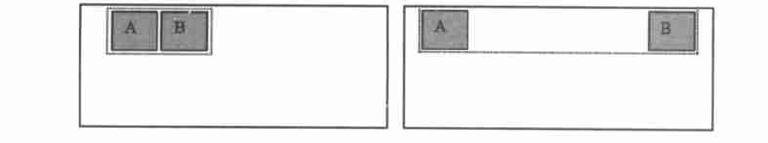

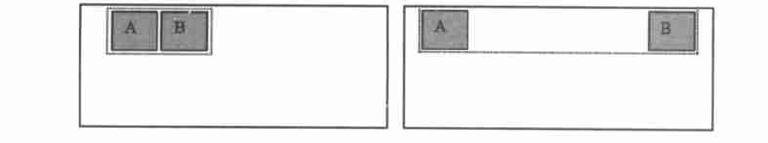

分析表明,在缺陷成团时,冗余容错电路的失效率取决于所对应成团因子的大小。成团因子决定于冗余容错电路的等效面积。冗余容错电路的等效面积等于涵盖整个冗余容错电路的最小面积,如图3所示。增大主、备份电路的几何距率,就是增大冗余容错电路的等效面积,从而增大对应成团因子的值。增大成团因子,就能降低冗余容错电路的失效率,提高其可靠性。

图3 冗余容错电路布局示意图

卫星电子系统的功能电路布局于FPGA内,功能电路由芯片内的若干简单逻辑块构成。为提高功能电路的可靠性,往往需要在片内对功能电路整体采取冗余容错措施,如最常用的单备份冗余容错形式。冗余容错电路包括主份电路、若干备份电路和切换电路,其可靠性是由主份电路、备份电路和切换电路共同决定的。如果主份和备份电路远比切换电路复杂,则可以忽略切换电路对冗余容错电路可靠性的影响,以下的讨论就是针对这一情况进行的。

对于冗余容错电路,不允许主份和备份电路都出现故障,引起冗余容错电路失效。因此有必要采取措施,尽可能降低冗余容错电路的失效率。

无论是FPGA内逻辑单元一类的简单逻辑块,还是处理器阵列中的处理器单元(PE)一类的复杂逻辑块,都可以采用成品率复合二项式分布模型分析其成品率。若把冗余容错电路的主份和备份电路分别看成是片内的一个复杂逻辑块,则可以用此模型分析缺陷成团对冗余容错电路可靠性产生的影响。

复合二项式分布模型的数学推导

经分析,式(3)给出的成品率复合二项式分布模型表达式存在错误,Stapper在文献中没有给出推导过程,因此首先从数学上对此模型进行了严格推导。推导的关键是利用Γ函数与B函数的关系:

缺陷成团对冗余容错电路可靠性影响分析

式(4)中的第三项对应n冗余容错电路的无故障概率Pn为

式(4) 中的第一项对应n 冗余容错电路的失效率Qn 为

分析式(5) 、(6) ,当参数u 趋近于无穷大时

当参数u 趋近于零时

式(7)、(8)表明,当参数u 趋近于无穷大时,Pn和Qn的值等于缺陷均匀分布时的值,说明此时缺陷不具备成团性,而是呈均匀分布状态; 式(9)、(10)表明,当参数u趋近于零时,Pn和Qn的值分别等于主份电路的可靠度和共效率。

参数u反映了IC 内部缺陷成团性的强弱,称为模型的成团因子。u 越大,缺陷成团性越弱;u 越小,缺陷成团性越强。

进一步分析表达式(5)、(6),对于任意的u>0 ,由于

所以有

。

缺陷成团时片内冗余容错电路的无故障概率和失效率比缺陷均匀分布时的都要高。缺陷成团性增大了冗余容错电路的失效率,削弱了冗余容错的可靠性增长功效。

多项式

,其值随参数u增大而增大,因此失效率Qn随参数u增大而减小,并且在u=0时取得最大值。成团因子u越大,冗余容错电路的失效率越低、可靠性就越高。这一结论对冗余容错电路可靠性设计具有重要指导意义。

成团因子

缺陷成团性强弱可以理解为缺陷相关性的强弱。缺陷成团性越强,缺陷相关性就越强,成团因子越小,反之亦然。若应用式(4)分析一个冗余容错电路,则成团因子反映的是冗余容错电。路内缺陷的平均相关度缺陷团面积是个随机值,当冗余容错电路面积小于最小缺陷团面积时,相应成团因子的值只取决于缺陷团内缺陷相关性的强弱,与冗余容错电路面积无关;当冗余容错电路面积大于最大缺陷团面积时,此时成团因子不仅受缺陷成团性强弱的影响,而且随冗余容错电路面积的变化而变化。

图2 成团因子α与冗余容错电路面积的关系

IC成品率预计常用到负二项式分布模型,此模型中的参数α是模型的成团因子。Stapper采用回归分析法分析验证成团因子α,得出成团因子与冗余容错电路面积的关系,如图2所示。曲线中的OA水平直线段表示α维持不变,对应冗余容错电路面积小于所有缺陷团面积的情况;曲线中的BC直线段表明α与冗余容错电路块面积成正比,对应冗余容错电路面积大于所有缺陷团面积的情况; 曲线中的AB曲线段表明α随冗余容错电路面积增大而呈现非线性增长,此时冗余容错电路面积介于最小缺陷团面积和最大缺陷团面积之间。

在没有缺陷团面积数据时,一般假定FPGA内缺陷团面积小至逻辑块,大至整个芯片,并且在这范围内连续分布。此时图2中的点A、B分别趋近点O、C,在曲线整个范围内,成团因子随冗余容错电路块面积增大而呈非线性增长。

实验数据表明,在冗余容错电路面积小于所有缺陷团面积时,成团成子u维持不变。成团因子α和u物理意义相同,遵循相似的变化规律。

缺陷成团时提高冗余容错电路可靠性的策略

冗余容错电路的主份和备份电路布局于FPGA芯片内。当FPGA内缺陷成团时,可以通过调整布局,增大主、备份电路的几何距离,降低冗余容错电路的失效率。

分析表明,在缺陷成团时,冗余容错电路的失效率取决于所对应成团因子的大小。成团因子决定于冗余容错电路的等效面积。冗余容错电路的等效面积等于涵盖整个冗余容错电路的最小面积,如图3所示。增大主、备份电路的几何距率,就是增大冗余容错电路的等效面积,从而增大对应成团因子的值。增大成团因子,就能降低冗余容错电路的失效率,提高其可靠性。

图3 冗余容错电路布局示意图

集成电路 FPGA 电路 电子 CPLD PCB 自动化 相关文章:

- 周立功:如何兼顾学习ARM与FPGA(05-23)

- 初学者如何学习FPGA(08-06)

- 为何、如何学习FPGA(05-23)

- FPGA 重复配置和测试的实现(08-14)

- 适用于消费性市场的nano FPGA技术(09-27)

- 赛灵思“授之以渔”理论:危机中如何巧降成本(06-04)