交换接口控制器的可扩展设计

时间:07-22

来源:互联网

点击:

专有FIC参考设计

专有FIC参考设计平台是采用英特尔的IXDP2401先进开发平台设计和验证的。AdvancedTCA机架把连接AdvancedTCA高速交换接口的两个IXMB2401网络处理器承载卡(carrier card)互连起来,承载卡是采用一块IXP2400处理器设计的PICMG3.x兼容板。承载卡采用标准组件结构,包含4个子卡槽位和一个可选交换接口子卡槽位,以便连接到AdvancedTCA背板上区域2的交换接口引脚。

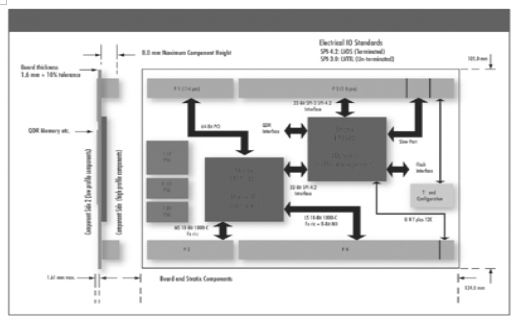

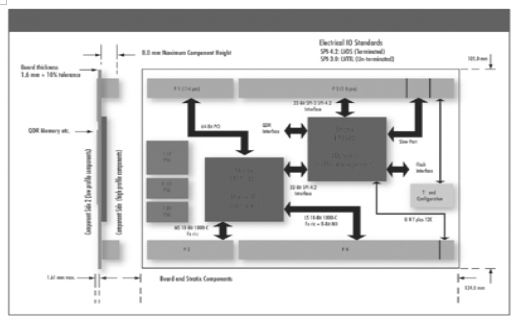

专有的、基于FPGA的交换接口子卡(mezzanine card)槽位的设计使其可插入承载卡,并提供一个可重配置的FIC和可选的流量管理开发板。FIC使处理器与AdvancedTCA交换结构相互连接。利用包含兼容PCI Express与XAUI的多通道收发器的可重复编程器件,可以提供可扩展的开发平台,以便快速设计和验证2.5Gbps到10Gbps的AdvancedTCA FIC设计(图6)。

工作模式

参考设计的主要工作模式接收来自处理器入口端的32位SPI3或16位SPI4.2数据,通过FPGA集成收发器将数据流传输到AdvancedTCA背板,并将背板数据流通过32位SPI3或16位SPI4.2接口传回处理器的出口端。

集成收发器经由处理器的SlowPort出口来配置。参考设计支持若干其它工作模式,包括SPI4.2接口环回、ASI接口环回、流量管理、交换结构数据包生成和监测。

FPGA和结构化ASIC FIC

采用专有的多FPGA和结构化ASIC技术,可以开发可扩展的PCI Express、ASI桥和端点。内建兼容PCI Express收发器的高密度、高性能的FPGA,可以提供:1. 具有可扩展的2.5链路的整体解决方案;2. 对每一个通道运行速率高达1Gbps的接口进行动态相位校正(DPA);3. 多种封装选择和高达40,000逻辑单元的密度选项。

图6:功能模块框图。

可选的FPGA结合独立的兼容PCI Express的SERDES,如PMC-Sierra的PM8358 QuadPHY 10GX器件可用于对成本的关注超过对性能和扩展功能需求的应用,从而提供低成本的1x、2x和4x(路)灵活的解决方案。高密度、高性能FPGA与独立的、兼容PCI Express的SERDES的结合,可被移植到专用的结构化ASIC,以提供所需要的最高密度、最快性能和最大数量的应用。

专有FIC参考设计平台是采用英特尔的IXDP2401先进开发平台设计和验证的。AdvancedTCA机架把连接AdvancedTCA高速交换接口的两个IXMB2401网络处理器承载卡(carrier card)互连起来,承载卡是采用一块IXP2400处理器设计的PICMG3.x兼容板。承载卡采用标准组件结构,包含4个子卡槽位和一个可选交换接口子卡槽位,以便连接到AdvancedTCA背板上区域2的交换接口引脚。

专有的、基于FPGA的交换接口子卡(mezzanine card)槽位的设计使其可插入承载卡,并提供一个可重配置的FIC和可选的流量管理开发板。FIC使处理器与AdvancedTCA交换结构相互连接。利用包含兼容PCI Express与XAUI的多通道收发器的可重复编程器件,可以提供可扩展的开发平台,以便快速设计和验证2.5Gbps到10Gbps的AdvancedTCA FIC设计(图6)。

工作模式

参考设计的主要工作模式接收来自处理器入口端的32位SPI3或16位SPI4.2数据,通过FPGA集成收发器将数据流传输到AdvancedTCA背板,并将背板数据流通过32位SPI3或16位SPI4.2接口传回处理器的出口端。

集成收发器经由处理器的SlowPort出口来配置。参考设计支持若干其它工作模式,包括SPI4.2接口环回、ASI接口环回、流量管理、交换结构数据包生成和监测。

FPGA和结构化ASIC FIC

采用专有的多FPGA和结构化ASIC技术,可以开发可扩展的PCI Express、ASI桥和端点。内建兼容PCI Express收发器的高密度、高性能的FPGA,可以提供:1. 具有可扩展的2.5链路的整体解决方案;2. 对每一个通道运行速率高达1Gbps的接口进行动态相位校正(DPA);3. 多种封装选择和高达40,000逻辑单元的密度选项。

图6:功能模块框图。

可选的FPGA结合独立的兼容PCI Express的SERDES,如PMC-Sierra的PM8358 QuadPHY 10GX器件可用于对成本的关注超过对性能和扩展功能需求的应用,从而提供低成本的1x、2x和4x(路)灵活的解决方案。高密度、高性能FPGA与独立的、兼容PCI Express的SERDES的结合,可被移植到专用的结构化ASIC,以提供所需要的最高密度、最快性能和最大数量的应用。

- 基于FPGA的片上系统的无线保密通信终端(02-16)

- 基于Virtex-5 FPGA设计Gbps无线通信基站(05-12)

- 基于FPGA的DVI/HDMI接口实现(05-13)

- 基于ARM的嵌入式系统中从串配置FPGA的实现(06-09)

- 采用EEPROM对大容量FPGA芯片数据实现串行加载(03-18)

- 赛灵思:可编程逻辑不仅已是大势所趋,而且势不可挡(07-24)