交换接口控制器的可扩展设计

时间:07-22

来源:互联网

点击:

ASI到SPI4.2的输出数据包流

在ASI到SPI4.2方向,采用可编程地址映射表(图2),从指定VC的交换结构输出的ASI TLP和流量等级被映射到16个SPI4.2通道中的一个。用户在VC到SPI4表中对VC到SPI4.2接口的通道映射信息进行编程。数据复用(MUX)记录表RAM(VCS4记录表RAM)包含从VC接口FIFO缓冲器读数据到把数据传送至SPI4.2接口的调度。VCS4记录表RAM有16个位置。

VCS4数据MUX和地址映射模块根据VCS4记录表RAM规定的顺序从VC FIFO通道读数据。SPI4.2源模块在必要时分拆队列并重组数据包,增加SPI4.2有效载荷控制操作,并通过SPI4.2接口将它们发往NPU。SPI4.2源模块也执行信用量管理,并根据从对等的SPI4.2接收器收到的流控制信息进行调度。

ASI提供若干协议接口(PI),它们提供可选功能或使各种协议适配到ASI基础架构。

协议接口描述

PI0封装被用于多播路由。为0的第二个PI表示生成树数据包,非0的第二个PI表示多播路由,多播组寻址通过多播组索引字段实现。

PI1将连接队列识别信息传递到下游对等交换单元或端点。当发生拥塞时,下游对等交换单元可以发送识别上游对等交换单元的违规连接队列的PI5拥塞管理消息。

PI2提供分段和重组(SAR)服务及封装。PI2报头包含有利于数据包描述的包起始(SOP)和包结束(EOP)信息。此外,PI2封装规定了可以在PI2容器内排列有效载荷数据的可选前置块(PPD)和末块(EPD)字节。

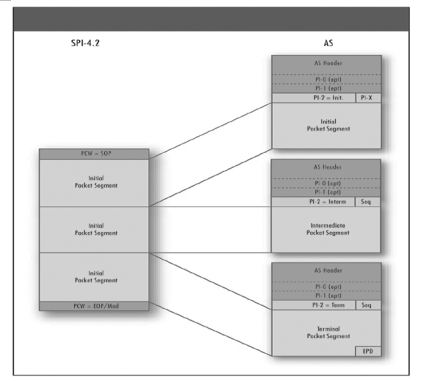

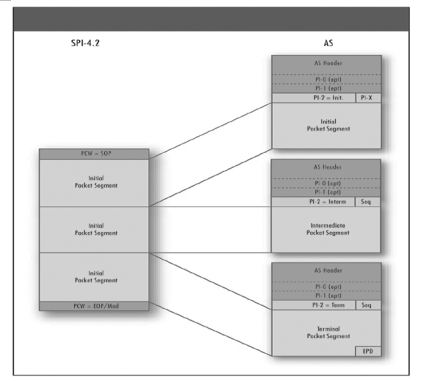

如果SPI4.2突发数据包长度与ASI TLP有效载荷长度相等的话(图3),PI2封装可以用于描述数据包并将数据流映射到关联域(Context)。此时,所接收到的SPI4.2突发数据已经被分段为ASI接口支持的有效载荷长度。因此,以数据包描述的观点来看,PI2仅仅需要表示SOP和EOP。

对于中间的突发数据,PI2 SAR代码就是“居中的”。注意,由于非EOP SPI4.2突发数据必须是多个16字节,所以中间数据包SPI4.2有效载荷将始终是32位排列,与ASI有效载荷匹配。

图4:在PI2分段的例子中,SPI4.2数据包被分为三个ASI TLP,去掉了SPI4.2协议控制字,对于每一个TLP,ASI报头要加上可选的PI0和PI1报头及PI2报头。

对于终端突发数据,如果在最后的TLP字中的所有字节都有效或与末块终接(terminal with end pad),则PI2 SAR代码就是“终端”,来表示最后的字中有效字节的数目。

如果SPI4.2突发数据包长度超过ASI TLP有效载荷长度的话,PI2 SAR被用于将SPI4.2数据包分段和重组。接收到的SPI4.2突发数据包在桥接中被分段为ASI接口支持的有效载荷的长度(图4)。

至于封装,三个TLP的PI2 SAR代码被分别设置为代表“初始”、“中间”和“终止”或“末块终接”。对于重组,来自每一个关联域的AS片段被重组成完整的数据包。一旦获得完整的数据包,它就被映射到一个SPI4.2通道并在突发数据包中输出。来自SPI4.2不同通道的突发数据包可以交织在一起。

映射流量类型、等级和目的端口

交换接口必须与数据一起传输若干重要属性。这些属性包括流量类型(单播或多播)、等级、目的端口和拥塞管理。这些参数都在AS中得到支持。然而,在SPI4.2中,该信息被映射在SPI4.2通道编号中或SPI4.2有效载荷内的专有报头。

SPI4.2利用三级拥塞指示(空虚、未满、饱满)进行基于信用量的流控制。通过预置与空虚和未满状态相对应的最大突发数据量(Maxburst1和Maxburst2),发送器会再次装满信用量。

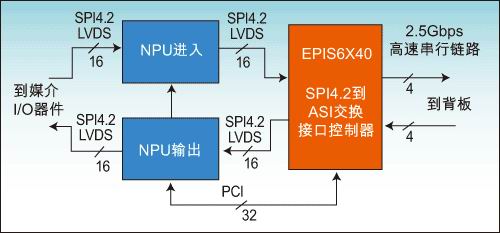

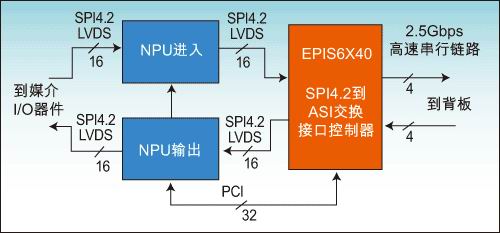

图5:典型单10Gbps端口中的双网络处理器及配备专用FIC的全双工线卡。

ASI具有多个流控制选项:VC,它是一个基于信用量的流控制;用于源速率控制的令牌桶;按照类或者流队列的基于状态的流控制。

桥接内的拥塞管理是桥接架构和缓冲机制的不可缺少的组成部分。桥接可以采用两种基本架构,或者采用具有很少或没有缓冲的直通(flow-through),或者每一个接口采用单级或两级缓冲。

在直通架构中,流控制信息被生成并在外部作用于桥上。该方法简化了桥的设计,但是,增加了源和流控制的目的端口之间的延迟时间,因此可能需要增加缓冲资源。

在有缓冲的架构中,桥接本身遵照流控制信息,因此需要内部缓冲。内部桥接缓冲可以由两个接口共享(单级),或每一个接口配备自己的关联缓冲器,称为两级缓冲处理。

入口网络处理器接收端口被配置为物理器件接口的SPI4,而发送端口被配置为交换接口的SPI4.2,连接到专有的FIC(图5)。FIC支持全双工SPI4.2接口和多达24个速率为2.5Gbps的全双工PCI Express SERDES(串行化/解串化)链路,一个10Gbps的全双工链路端口需要4个SERDES链路。不用的SERDES链路可以通过器件配置寄存器的设置来关闭供电。在这个10Gbps的例子中,NPU通过PCI本地总线接口配置EP1SGX40内部的“配置和状态”寄存器。

在ASI到SPI4.2方向,采用可编程地址映射表(图2),从指定VC的交换结构输出的ASI TLP和流量等级被映射到16个SPI4.2通道中的一个。用户在VC到SPI4表中对VC到SPI4.2接口的通道映射信息进行编程。数据复用(MUX)记录表RAM(VCS4记录表RAM)包含从VC接口FIFO缓冲器读数据到把数据传送至SPI4.2接口的调度。VCS4记录表RAM有16个位置。

VCS4数据MUX和地址映射模块根据VCS4记录表RAM规定的顺序从VC FIFO通道读数据。SPI4.2源模块在必要时分拆队列并重组数据包,增加SPI4.2有效载荷控制操作,并通过SPI4.2接口将它们发往NPU。SPI4.2源模块也执行信用量管理,并根据从对等的SPI4.2接收器收到的流控制信息进行调度。

ASI提供若干协议接口(PI),它们提供可选功能或使各种协议适配到ASI基础架构。

协议接口描述

PI0封装被用于多播路由。为0的第二个PI表示生成树数据包,非0的第二个PI表示多播路由,多播组寻址通过多播组索引字段实现。

PI1将连接队列识别信息传递到下游对等交换单元或端点。当发生拥塞时,下游对等交换单元可以发送识别上游对等交换单元的违规连接队列的PI5拥塞管理消息。

PI2提供分段和重组(SAR)服务及封装。PI2报头包含有利于数据包描述的包起始(SOP)和包结束(EOP)信息。此外,PI2封装规定了可以在PI2容器内排列有效载荷数据的可选前置块(PPD)和末块(EPD)字节。

如果SPI4.2突发数据包长度与ASI TLP有效载荷长度相等的话(图3),PI2封装可以用于描述数据包并将数据流映射到关联域(Context)。此时,所接收到的SPI4.2突发数据已经被分段为ASI接口支持的有效载荷长度。因此,以数据包描述的观点来看,PI2仅仅需要表示SOP和EOP。

对于中间的突发数据,PI2 SAR代码就是“居中的”。注意,由于非EOP SPI4.2突发数据必须是多个16字节,所以中间数据包SPI4.2有效载荷将始终是32位排列,与ASI有效载荷匹配。

图4:在PI2分段的例子中,SPI4.2数据包被分为三个ASI TLP,去掉了SPI4.2协议控制字,对于每一个TLP,ASI报头要加上可选的PI0和PI1报头及PI2报头。

对于终端突发数据,如果在最后的TLP字中的所有字节都有效或与末块终接(terminal with end pad),则PI2 SAR代码就是“终端”,来表示最后的字中有效字节的数目。

如果SPI4.2突发数据包长度超过ASI TLP有效载荷长度的话,PI2 SAR被用于将SPI4.2数据包分段和重组。接收到的SPI4.2突发数据包在桥接中被分段为ASI接口支持的有效载荷的长度(图4)。

至于封装,三个TLP的PI2 SAR代码被分别设置为代表“初始”、“中间”和“终止”或“末块终接”。对于重组,来自每一个关联域的AS片段被重组成完整的数据包。一旦获得完整的数据包,它就被映射到一个SPI4.2通道并在突发数据包中输出。来自SPI4.2不同通道的突发数据包可以交织在一起。

映射流量类型、等级和目的端口

交换接口必须与数据一起传输若干重要属性。这些属性包括流量类型(单播或多播)、等级、目的端口和拥塞管理。这些参数都在AS中得到支持。然而,在SPI4.2中,该信息被映射在SPI4.2通道编号中或SPI4.2有效载荷内的专有报头。

SPI4.2利用三级拥塞指示(空虚、未满、饱满)进行基于信用量的流控制。通过预置与空虚和未满状态相对应的最大突发数据量(Maxburst1和Maxburst2),发送器会再次装满信用量。

图5:典型单10Gbps端口中的双网络处理器及配备专用FIC的全双工线卡。

ASI具有多个流控制选项:VC,它是一个基于信用量的流控制;用于源速率控制的令牌桶;按照类或者流队列的基于状态的流控制。

桥接内的拥塞管理是桥接架构和缓冲机制的不可缺少的组成部分。桥接可以采用两种基本架构,或者采用具有很少或没有缓冲的直通(flow-through),或者每一个接口采用单级或两级缓冲。

在直通架构中,流控制信息被生成并在外部作用于桥上。该方法简化了桥的设计,但是,增加了源和流控制的目的端口之间的延迟时间,因此可能需要增加缓冲资源。

在有缓冲的架构中,桥接本身遵照流控制信息,因此需要内部缓冲。内部桥接缓冲可以由两个接口共享(单级),或每一个接口配备自己的关联缓冲器,称为两级缓冲处理。

入口网络处理器接收端口被配置为物理器件接口的SPI4,而发送端口被配置为交换接口的SPI4.2,连接到专有的FIC(图5)。FIC支持全双工SPI4.2接口和多达24个速率为2.5Gbps的全双工PCI Express SERDES(串行化/解串化)链路,一个10Gbps的全双工链路端口需要4个SERDES链路。不用的SERDES链路可以通过器件配置寄存器的设置来关闭供电。在这个10Gbps的例子中,NPU通过PCI本地总线接口配置EP1SGX40内部的“配置和状态”寄存器。

- 基于FPGA的片上系统的无线保密通信终端(02-16)

- 基于Virtex-5 FPGA设计Gbps无线通信基站(05-12)

- 基于FPGA的DVI/HDMI接口实现(05-13)

- 基于ARM的嵌入式系统中从串配置FPGA的实现(06-09)

- 采用EEPROM对大容量FPGA芯片数据实现串行加载(03-18)

- 赛灵思:可编程逻辑不仅已是大势所趋,而且势不可挡(07-24)