基于FPGA的液晶显示驱动IP核的实现

时间:07-24

来源:互联网

点击:

引言

液晶显示驱动有多种方法,通常采用的方法为基于专用集成电路的方法和基于通用微处理器的方法。本文研究了一种基于FPGA (EP1K30QC208-3)的液晶显示驱动方法,与专用集成电路比, FPGA 更灵活;与通用微处理器相比, FPGA 的速度更快。利用硬件描述语言,编制了液晶显示驱动的IP核,开发了32×32 可变宽度像素点的液晶显示驱动电路,指出,基于FPGA的驱动方法能够满足液晶显示驱动时序上的要求,且具有控制灵活的特点,在外扩片外SRAM 或SDRAM 后,容易移植在更多可变宽度像素点的液晶显示器的驱动上。因FPGA 液晶显示驱动器的像素时钟为25.175MHz ,普通的单片机难以满足要求,故选用ALTERA 公司的ACEX 系列FPGA 作为驱动电路的核心部件。FPGA即现场可编程门阵列器件,是一种超大规模集成电路,具有在电路可重配置能力(in circuit reconfigurable , ICR) 。设计者设计的逻辑在编译、适配后变成网络表,下载到FPGA 芯片上之后, FPGA 即可执行设计逻辑的功能。因此,FPGA 非常适合于进行快速原型设计,设计者可完全控制产品开发过程中由逻辑设计到最终产品的全过程。

设计与实现

本液晶显示屏采用了商用的CJM10C11 系列TFT 液晶显示屏,该显示屏是一种用非晶硅作为开关器件的有源矩阵液晶显示器,其接口为TTL 电平,分辨率为640×480 像素,像素尺寸为100μm×300μm ,灰度级为64级灰度,用18bit数据信号能显示262144 色。

图1 液晶显示驱动系统总体框图

液晶显示驱动电路总体框图如图1 所示。驱动电路通过串口和上位机进行通讯,数据通过串口传输到FPGA 的片上ROM 中,传输结束后FPGA 上的液晶显示驱动电路开始工作,控制信号发生器产生控制信号及地址, 并将由片上ROM 读出的各可变宽度像素点的灰度值送LCD显示器显示。在本方案中,与上位机的串行接口、片上ROM、像素时钟发生器以及控制信号发生器都是在一片FPGA (ACEX1 K30) 上实现的。

ACEX 系列的FPGA 由排成行和列的逻辑阵列块LAB (logic array block) 、每行之中嵌入的嵌入式阵列块EAB (embedded array block) 、快速互连以及IO 单元构成。每个逻辑阵列块包含8 个逻辑单元LE (logic element ) 和一个局部互联。每个逻辑单元则由一个4 输入查找表(LUT) ,一个可编程触发器,快速进位链、级连链组成,多个LAB和多个EAB通过快速通道互相连接。嵌入式阵列块是ACEX 系列器件在结构设计上的一个重要部件。它是输入端口和输出端口都带有触发器的一种灵活的RAM块,其主要功能就是实现一些规模不太大的FIFO、ROM、RAM 和双端口RAM 等。

在本液晶显示驱动电路中,主要用宏功能模块实现片上ROM ,它调用FPGA 上的EAB 资源实现灰度数据的存储,用普通的逻辑单元存储坐标值,实现可变宽度像素的像素宽度存储。在ACEX1K30 中,共有6块4096 位的EAB 资源,可实现45×45 可变宽度像素的18 bit 灰度显示。另外,在综合时,计数器、加法器等逻辑器件能够调用FPGA 上的快速进位链等资源,提高设计的性能。液晶显示器显示方案如图2所示,整个图像分为消隐区和可视区,在可视区中划分出32×32可变宽度像素的控制显示区,每个可变宽度像素中是由n×n个像素构成的。当扫描点位于可视区内,控制显示区外时,所显示的灰度为0;当扫描信号进入控制显示区后,根据控制信号发生器所产生的地址值,由ROM 中读取灰度值,送LCD显示器进行显示。控制显示区在可视区中的坐标以及每个可变宽度像素的宽度,即行或列方向上的像素数都是独立可调的,具有很强的灵活性。

图2 液晶显示器显示方案

像素时钟发生器

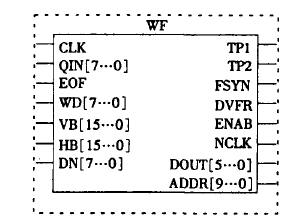

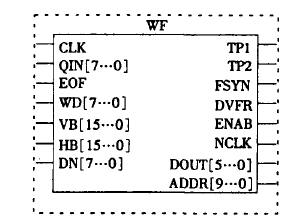

像素时钟发生器是LCD 液晶显示器驱动IP核中显示和控制信号发生器的基准。该显示屏的时序信号为由水平和垂直视频时序组合而成的复合视频时序。像素时钟频率为25.175MHz ,像素时钟周期为39.72ns ,行显示时间为640个时钟周期,行消隐时间为160个时钟周期,每个视频行为800 个时钟周期,帧显示时间为480个视频行周期,帧消隐时间为45个视频行周期。在FPGA中,将像素时钟发生器和控制信号发生器组合在同一个控制模块WF 中,用硬件描述语言VHDL实现了该液晶显示驱动IP 核,如图3 所示。CLK脚接25.175 MHz 晶振,产生液晶显示屏所需要的像素时钟。控制行、帧显示及消隐的二进制计数器在行、帧消隐期间复位,在行、帧显示期间开始工作,并产生控制信号发生器所需要的信号。

图3 液晶显示器驱动IP核

控制信号发生器

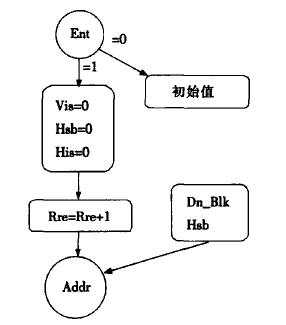

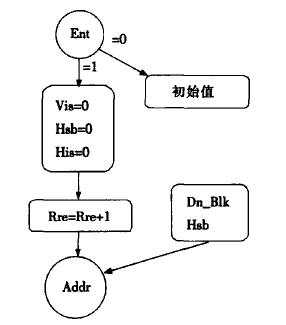

控制信号发生器最主要的部分是地址产生器,它根据水平和垂直显示及消隐计数器的值产生控制信号,其状态机如图4 所示。液晶显示驱动器驱动电路工作后,首先由ROM中读入控制显示区的参照点坐标、控制显示区每行中的可变宽度像素数、可变宽度像素的宽度等数据,在水平显示及垂直显示时间, 将水平显示与垂直显示计数器中的值与这些数据进行比较,判定是否进入控制显示区域,需要进行显示。如未进入控制显示区域,即Ent = 0 ,则灰度值为0 ,若Ent = 1 则水平、垂直的可变宽度像素计数器和像素计数器开始计数,如垂直的像素计数器Vis、水平的可变宽度像素计数器Hsb 和水平的像素计数器His 都为零,则表示已扫描到一行可变宽度像素的最后一个像素,触边计数器Rre计数值加1 。根据触边计数器、水平可变宽度像素计数器以及每行中的可变宽度像素数(为常数,本文中为32) ,可确定地址Addr的值。通过此地址即可由ROM 中读出灰度值,送到TFT 液晶显示屏后就可以控制每个可变宽度像素的灰度值,即加在每个像素的两极的电压,从而实现可变坐标、可变像素宽度、可变灰度的显示。

图4 控制信号发生器状态机

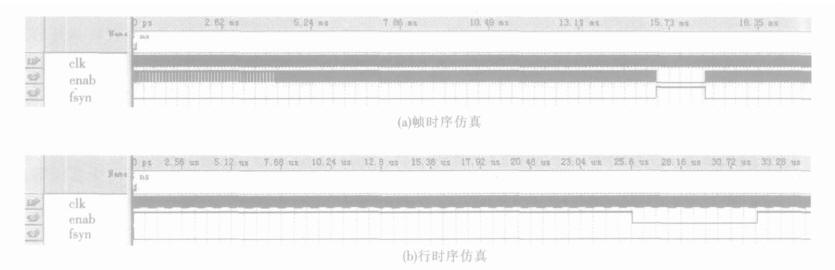

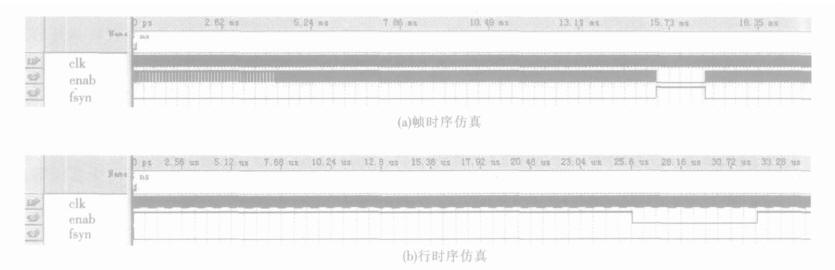

液晶显示驱动IP 核的仿真结果如图5 所示,其中enab 为复合同步信号,fsyn 为帧同步信号。该IP 核在QuartusII 4.2 下编译通过,占用1K30-3中的458个LE ,最高时钟频率为25.71 MHz ,满足设计要求。

图5 帧、行时序仿真结果

液晶显示驱动有多种方法,通常采用的方法为基于专用集成电路的方法和基于通用微处理器的方法。本文研究了一种基于FPGA (EP1K30QC208-3)的液晶显示驱动方法,与专用集成电路比, FPGA 更灵活;与通用微处理器相比, FPGA 的速度更快。利用硬件描述语言,编制了液晶显示驱动的IP核,开发了32×32 可变宽度像素点的液晶显示驱动电路,指出,基于FPGA的驱动方法能够满足液晶显示驱动时序上的要求,且具有控制灵活的特点,在外扩片外SRAM 或SDRAM 后,容易移植在更多可变宽度像素点的液晶显示器的驱动上。因FPGA 液晶显示驱动器的像素时钟为25.175MHz ,普通的单片机难以满足要求,故选用ALTERA 公司的ACEX 系列FPGA 作为驱动电路的核心部件。FPGA即现场可编程门阵列器件,是一种超大规模集成电路,具有在电路可重配置能力(in circuit reconfigurable , ICR) 。设计者设计的逻辑在编译、适配后变成网络表,下载到FPGA 芯片上之后, FPGA 即可执行设计逻辑的功能。因此,FPGA 非常适合于进行快速原型设计,设计者可完全控制产品开发过程中由逻辑设计到最终产品的全过程。

设计与实现

本液晶显示屏采用了商用的CJM10C11 系列TFT 液晶显示屏,该显示屏是一种用非晶硅作为开关器件的有源矩阵液晶显示器,其接口为TTL 电平,分辨率为640×480 像素,像素尺寸为100μm×300μm ,灰度级为64级灰度,用18bit数据信号能显示262144 色。

图1 液晶显示驱动系统总体框图

液晶显示驱动电路总体框图如图1 所示。驱动电路通过串口和上位机进行通讯,数据通过串口传输到FPGA 的片上ROM 中,传输结束后FPGA 上的液晶显示驱动电路开始工作,控制信号发生器产生控制信号及地址, 并将由片上ROM 读出的各可变宽度像素点的灰度值送LCD显示器显示。在本方案中,与上位机的串行接口、片上ROM、像素时钟发生器以及控制信号发生器都是在一片FPGA (ACEX1 K30) 上实现的。

ACEX 系列的FPGA 由排成行和列的逻辑阵列块LAB (logic array block) 、每行之中嵌入的嵌入式阵列块EAB (embedded array block) 、快速互连以及IO 单元构成。每个逻辑阵列块包含8 个逻辑单元LE (logic element ) 和一个局部互联。每个逻辑单元则由一个4 输入查找表(LUT) ,一个可编程触发器,快速进位链、级连链组成,多个LAB和多个EAB通过快速通道互相连接。嵌入式阵列块是ACEX 系列器件在结构设计上的一个重要部件。它是输入端口和输出端口都带有触发器的一种灵活的RAM块,其主要功能就是实现一些规模不太大的FIFO、ROM、RAM 和双端口RAM 等。

在本液晶显示驱动电路中,主要用宏功能模块实现片上ROM ,它调用FPGA 上的EAB 资源实现灰度数据的存储,用普通的逻辑单元存储坐标值,实现可变宽度像素的像素宽度存储。在ACEX1K30 中,共有6块4096 位的EAB 资源,可实现45×45 可变宽度像素的18 bit 灰度显示。另外,在综合时,计数器、加法器等逻辑器件能够调用FPGA 上的快速进位链等资源,提高设计的性能。液晶显示器显示方案如图2所示,整个图像分为消隐区和可视区,在可视区中划分出32×32可变宽度像素的控制显示区,每个可变宽度像素中是由n×n个像素构成的。当扫描点位于可视区内,控制显示区外时,所显示的灰度为0;当扫描信号进入控制显示区后,根据控制信号发生器所产生的地址值,由ROM 中读取灰度值,送LCD显示器进行显示。控制显示区在可视区中的坐标以及每个可变宽度像素的宽度,即行或列方向上的像素数都是独立可调的,具有很强的灵活性。

图2 液晶显示器显示方案

像素时钟发生器

像素时钟发生器是LCD 液晶显示器驱动IP核中显示和控制信号发生器的基准。该显示屏的时序信号为由水平和垂直视频时序组合而成的复合视频时序。像素时钟频率为25.175MHz ,像素时钟周期为39.72ns ,行显示时间为640个时钟周期,行消隐时间为160个时钟周期,每个视频行为800 个时钟周期,帧显示时间为480个视频行周期,帧消隐时间为45个视频行周期。在FPGA中,将像素时钟发生器和控制信号发生器组合在同一个控制模块WF 中,用硬件描述语言VHDL实现了该液晶显示驱动IP 核,如图3 所示。CLK脚接25.175 MHz 晶振,产生液晶显示屏所需要的像素时钟。控制行、帧显示及消隐的二进制计数器在行、帧消隐期间复位,在行、帧显示期间开始工作,并产生控制信号发生器所需要的信号。

图3 液晶显示器驱动IP核

控制信号发生器

控制信号发生器最主要的部分是地址产生器,它根据水平和垂直显示及消隐计数器的值产生控制信号,其状态机如图4 所示。液晶显示驱动器驱动电路工作后,首先由ROM中读入控制显示区的参照点坐标、控制显示区每行中的可变宽度像素数、可变宽度像素的宽度等数据,在水平显示及垂直显示时间, 将水平显示与垂直显示计数器中的值与这些数据进行比较,判定是否进入控制显示区域,需要进行显示。如未进入控制显示区域,即Ent = 0 ,则灰度值为0 ,若Ent = 1 则水平、垂直的可变宽度像素计数器和像素计数器开始计数,如垂直的像素计数器Vis、水平的可变宽度像素计数器Hsb 和水平的像素计数器His 都为零,则表示已扫描到一行可变宽度像素的最后一个像素,触边计数器Rre计数值加1 。根据触边计数器、水平可变宽度像素计数器以及每行中的可变宽度像素数(为常数,本文中为32) ,可确定地址Addr的值。通过此地址即可由ROM 中读出灰度值,送到TFT 液晶显示屏后就可以控制每个可变宽度像素的灰度值,即加在每个像素的两极的电压,从而实现可变坐标、可变像素宽度、可变灰度的显示。

图4 控制信号发生器状态机

液晶显示驱动IP 核的仿真结果如图5 所示,其中enab 为复合同步信号,fsyn 为帧同步信号。该IP 核在QuartusII 4.2 下编译通过,占用1K30-3中的458个LE ,最高时钟频率为25.71 MHz ,满足设计要求。

图5 帧、行时序仿真结果

集成电路 FPGA 电路 显示器 单片机 LTE 快速原型 信号发生器 LCD 嵌入式 VHDL 电压 仿真 Quartus 相关文章:

- 周立功:如何兼顾学习ARM与FPGA(05-23)

- 初学者如何学习FPGA(08-06)

- 为何、如何学习FPGA(05-23)

- FPGA 重复配置和测试的实现(08-14)

- 适用于消费性市场的nano FPGA技术(09-27)

- 赛灵思“授之以渔”理论:危机中如何巧降成本(06-04)