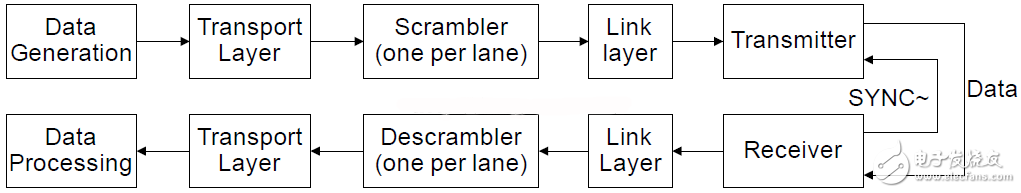

数据链路层发送与接收的处理过程及涉及到的模块

Asserted by receiver to indicate that the current symbol is a valid symbol given the current running disparity.

1.5 Scrambler and Descrambler

加扰编码和解扰编码存在JESD204 TX和RX的模块中,并可以通过控制字使能是否对数据流进行加扰。

加扰模块都是针对单独的数据通道,不会出现不同数据通道的数据混合加扰的情况,也就是说每一个数据通道有自己独立的加扰通道。

加扰编码模块的功能是为了增加数据流中的高频分量,减小数据流中连续0和1的个数。如果出现长时间的连续"1"或连续"0",会影响接收端从数字信号中提取时钟。

图28: Functional location of scrambler and descrambler

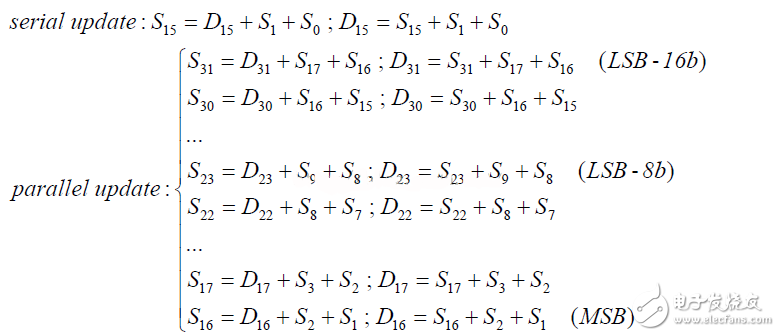

1.5.1 加扰公式

1+x[14]+x[15]

该公式的作用周期可以长达32767bit,非常适合对频谱敏感的收发应用,而解扰器只需要2个字节缓存就能解扰。

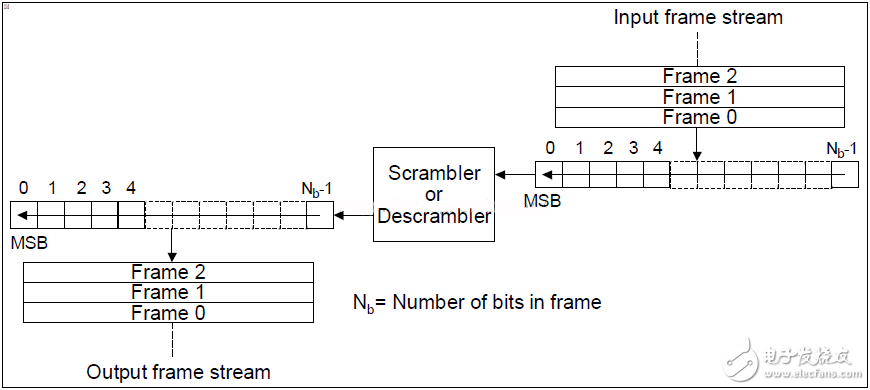

1.5.2 加扰的流程

加扰器解扰器都是通过数据流串行输入实现的,最小的处理单位为帧,加扰与解扰的顺序是由高位到低位。具体的流程如下图所示:

图29:Serial scrambling

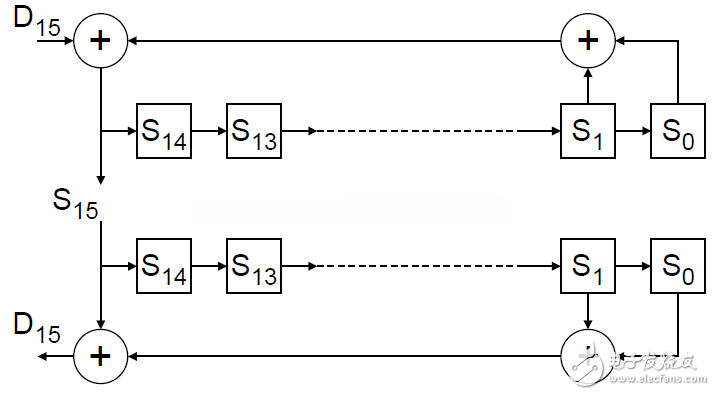

1.5.3 加扰的方式

加扰的实现方式可以分为两种,串行加扰和并行加扰,串行加扰的时钟域为发送接口的串行时钟速率,虽然串行的加扰方式实现简单,但是工作的频率很高,RTL的实现难度要大于并行加扰模式,因此设计中采用并行加扰模式。

串行加扰和并行加扰的流程图如下图所示:

图30:Serial scrambler anddescrambler implementation

scrambler模块加入了使能信号,其结构如下图所示,当en信号无效时,scrambler模块将会被bypass,同时在code group synchronization sequence和transmission of an initial lane alignment sequence发送时,scrambler也是bypass的。在使能scrambler后,scrambler和descramber模块将会有两个octet的数据延迟。

1.6 8b/10 Encoder andDecoder/monitoring

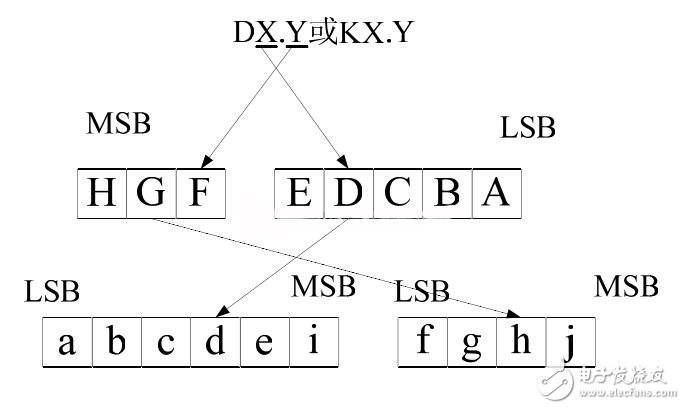

8b/10b编码的原理是将一组连续的8位数据分解成两组数据,一组3位,一组5位,经过编码后分别成为一组4位的代码和一组6位的代码,从而组成一组10位的数据发送出去。相反,解码是将一组10位的输入数据经过变换得到8位数据位。数据值可以统一的表示为DX.Y或KX.Y,其中D表示为数据代码,K表示为特殊的命令代码。X表示输入的原始数据的低5位EDCBA,Y表示输入的原始数据的高3位HGF。因此8b/10b编码逻辑可分解为两个子逻辑块,一个5b/6b编码器(EDCBA<—>iedcba)和一个3b/4b编码器(HGF<—>jhgf)。编码原理图如下图所示。

图30:8b/10 Encoder and Decoder

在8b/10b编码过程中,会出现字符不一致的情况,即一组字符中"1"和"0"的个数不一致的情况,这种情况称作差异度。当字符中的"0"比"1"多时,称作负极性;"1"比"0"多时,称作正极性;"0"和"1"相等时,为零极性。编码规则规定,非零极性的编码结果(包括4位结果,6位结果和组合的10位结果)的极性必须依次翻转[1]。比如,如果6位编码结果具有正的极性,则接下来的4位结果应该具有负的极性,如果接下来的4位结果具有零极性,则继续要求4位结果后面6位结果具有负的极性,以此类推。

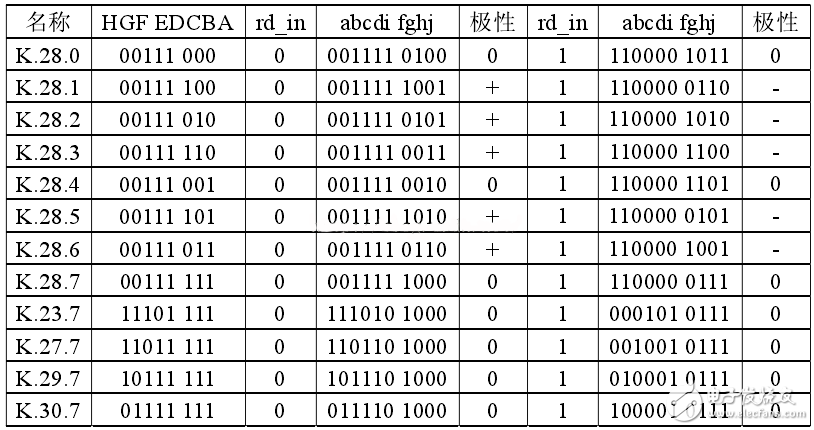

1.6.1 K_encode模块设计

控制字在 8b/10b 编码中只有 12 组,可以整体查表的方法实现:

表10:8b/10b 编码K码

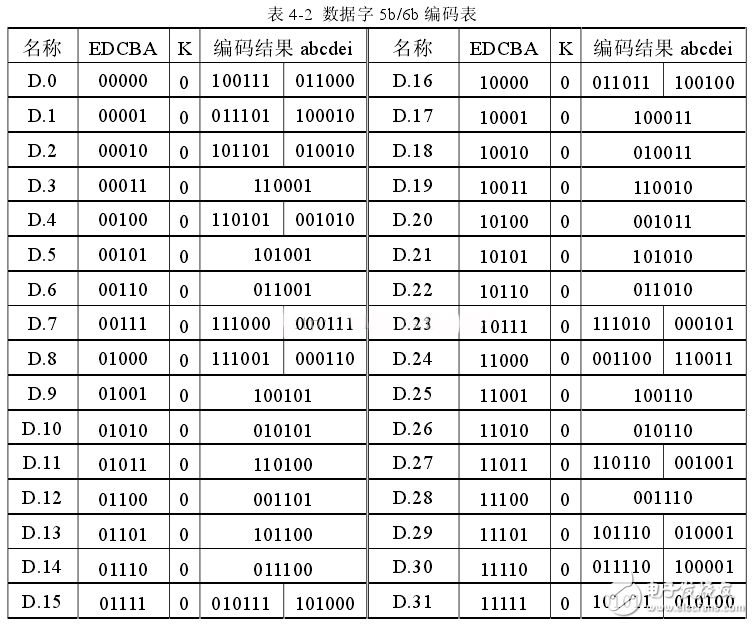

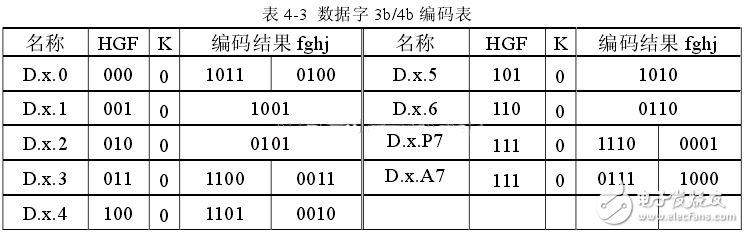

1.6.2 D_encode 模块设计

数据字编码共有 256 组,通常将其划分为 3b/4b 编码和 5b/6b 编码分别进行编码,5b/6b 和 3b/4b 编码表如表 4-2 和 4-3 所示。编码结果栏目下,编码结果为中性的只有 1 列,编码结果极性不平衡的,分成了两列,左边一列的编码结果具有正极性,右边一列的编码结果具有负极性。

表11:8b/10b 编码D码表

编码表中有两点需要注意:

1、表 4-2 中的 D.7 和表 4-3 中 D.x.3 的编码结果,其编码结果中"1"与"0"的个数相等,它本身是零极性的,但是其编码结果却有两种可能;

2、表 4-3 中输入为 D.x.7 的编码结果可能四种:1110、0001、0111 和 1000,

做出这样规定的目的是为了消除编码结果 eifgh 出现 5 个连续"1"或者"0"的情况。

表12:8b/10b 编码D码表

1.6.3 Comma 检测原理

SerDes 接口在发送端将字节信息经过编码和串并转换后,经过信道传输到接收机上,接收机对收到的串行码流进行重定时,并把它们重新恢复成并行的字节数据。Comma 信号就是用来指示字节边界,获取和验证字节同步(ByteSynchronization)的。为了有效达到这个目的,Comma 信号必须具有以下两个特性:它必须是独一无二的

- 用于以太网物理层时钟同步PLL的VCO设计(04-01)

- CAN物理层调试基础知识及举例(02-07)

- 与USB3.1相比,新规范--速率再翻倍(09-09)

- 高线性度组件简化直接转换接收器的设计(08-12)

- 半英寸 UMTS 基站接收器(10-08)

- 纤巧的数字预失真接收器集成了 RF、滤波器和 ADC(04-10)