纤巧的数字预失真接收器集成了 RF、滤波器和 ADC

在蜂窝基站中,功率放大器 (PA) 消耗的电功率比其他任何组件都多,因此就服务提供商而言, PA 是增大运营支出的一个重要因素。复杂的数字调制方法要求 PA 具有极高的线性,因此必须在远低于饱和区的范围内驱动功率放大器,在这个区域内, PA 的效率最高。为了提高 PA 的效率,设计师使用了数字技术,以降低波峰因数,并改善 PA 的线性度,从而允许 PA 在靠近饱和区的范围内工作。数字预失真 (DPD) 是首选的 PA 线性化方法。数字预失真算法受到了大量关注,不过还有一个关键组件,即 RF 反馈接收器。

数字预失真接收器的要求

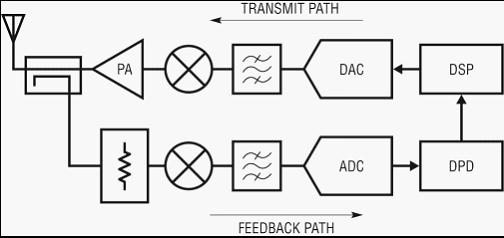

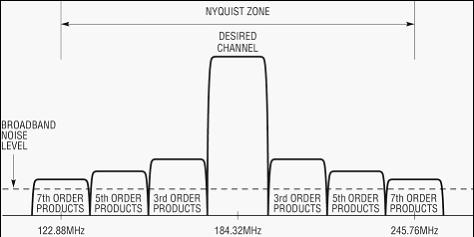

数字预失真接收器将 PA 的输出从 RF 信号转换回数字信号,是反馈环路的一部分 (参见图 1) 。关键设计要求是,输入频率范围和功率大小、中频以及要数字化的带宽。在这些要求中,有些可以直接从 PA 的性能规范中得出,有些是在设计时优化的。基带发送信号被上变频至载频,并被限定在由 WCDMA、TD-SCDMA、CDMA2000、LTE 等空中接口标准所规定的频段内。由于 DPD 环路的用途是测量 PA 传递函数,因而不必分离载频或对数字数据进行解调。PA 非线性将产生奇数阶的互调分量,这些分量会在相邻通道和交替通道中形成频谱增生。3 阶分量出现在 3 倍于期望通道带宽的范围之内 (见图 2)。同样,5 阶分量和 7 阶分量则分别处在 5 倍和 7 倍于期望通道带宽的范围以内。因此,DPD 接通器必须获得一个与正在进行线性化处理的互调分量之阶数相等的发送带宽倍数。

图 1:数字预失真信号链路

图 2:互调分量

目前的开发趋势是将所需通道混频至中频 (IF) ,并捕获所有互调分量的全部带宽。要准确选择中频以减轻滤波负担,并避开按照规范要求已经确定的其他频率。类似地,采样率也要选择为数字调制芯片速率的倍数,例如,在 WCDMA 情况下为 3.84MHz。最后,奈奎斯特 (Nyquist) 定理要求,采样率必须至少是采样带宽的 2 倍。尽管很多配置都是可接受的,但是这里仅列出一组满足这些限制的配置,中频为 184.32MHz,ADC 采样率为 245.76MHz,带宽为 122.88MHz。

在 20W PA 的情况下,平均输出功率是 43dBm。峰值对平均值之比 (PAR) 约为 15dBm。为了将接收链路混频器的平均输入功率设定为 -15dBm,耦合器和衰减器合起来的插入损耗必须是 58dB (参见图 1)。WCDMA 标准规定, PA 的带内噪声最大为 -13dBm/MHz (-73dBm/Hz)。因此,耦合器和衰减器 (-58dB) 及 PA 噪声限制 (-13dBm/MHz) 合起来,要求接收器灵敏度必须低于 -71dBm/MHz (-131dBm/Hz)。为了提供充足的裕度,至少需要比这个值好 6dB 至 10dB 的数值。这就为数字预失真接收器设定了频率计划、功率大小和灵敏度要求。

集成的数字预失真接收器

一旦确定了系统要求,便可着手采用一个混频器、IF 放大器、ADC、无源滤波、匹配网络和电源旁路来实作电路。尽管计算和仿真很有用,但无可替代的是对真实硬件的评估,这种评估一般会导致印刷电路板 (PCB) 的多次迭代。不过,基于凌力尔特微型模块 (µModule®) 封装技术的新一类集成式接收器极大地简化了这个任务。LTM®9003 数字预失真 µModule 接收器是一款全面集成的数字预失真接收器,尤其是在单个器件中完成了 RF 至数字信号的转换。

LTM9003 由高线性度有源混频器、中频放大器、L-C 带通滤波器和高速 ADC 组成 (参见图 3)。导线连接的裸片组装确保总体外形尺寸非常紧凑,但与传统封装可能做到的相比,仍然允许基准和电源旁路电容器放置在更加靠近芯片的地方。这减少了噪声使 ADC 保真度降低的可能性。这一理念应用到了 LTM9003 接收器链路中到处都在使用的高频布局方法中。

数字预失真 μModule接收器 LTM9003 相关文章: