用于以太网物理层时钟同步PLL的VCO设计

摘要:研究了一种基于以太网物理层时钟同步的高带宽低噪声压控振荡器(VCO),该VCO采用交叉耦合的电流饥饿型环形振荡器,通过级联11级环路电路和改善其控制电压变换电路,优化了VCO的输出频率范围以及降低了输出时钟的相位噪声,完全满足以太网物理层芯片时钟电路的性能指标。基于TSMC 3.3 V 0.25 μm CMOS工艺的仿真结果表明,中心频率为250 MHz时,压控增益为300 MHz/V,其线性区覆盖范围是60~480 MHz,在偏离中心频率600 kHz处的相位噪声为-108 dBc。

关键词:VCO;环形振荡器;电流饥饿型;时钟同步

0 引言

在以太网中,物理层芯片(Physical Layer Interface Devices,PHY)是将各网元连接到物理介质上的关键部件。负责完成互连参考模型(OSI)第I层中的功能,即为链路层实体之间进行位传输提供物理连接所需的机械、电气、光电转换和规程手段。其功能包括建立、维护和拆除物理电路,实现物理层比特(bit)流的透明传输等。物理层包括4个功能层和两个上层接口。两个上层接口为物理介质无关层接口(MII)和物理介质相关层接口(MDI),在MII的上层是逻辑数据链路层(DLL),而MDI的下层则直接与传输介质相连。而这些子层的正常工作都离不开一个稳定精确的时钟同步信号。PLL在物理层芯片的时钟同步应用中,要求其输出时钟带宽覆盖范围广,电压控制频率线性度好,频谱纯度高。在PLL设计过程中,VCO是最为关键的设计环节,其性能将直接决定PLL的设计工作质量。近年来,VCO相位噪声得到越来越深入的研究,各种低噪声VCO结构不断涌现,文献中提到的交叉耦合电流饥饿型VCO便是其中一种。电流饥饿是指电路单元的电流受到电流源的钳制而不能达到其应有的最大值。本文在其基础上采用了一种有效控制电压变换电路,保证原有电路优点的同时扩展了线性度,提高抗噪声能力,有效降低了相位噪声。

1 VCO延迟单元工作原理

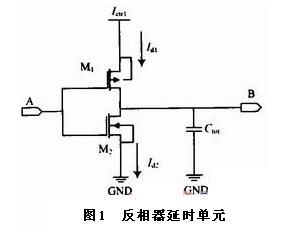

图1所示为电流饥饿型VCO中的单级结构。PNP管M1和NPN管M2是延迟单元的组成部分,Ictrl是用于控制电容的放电电流Id1和充电电流Id2,他们是构成环形振荡器的每一级。Ictrl控制着流过M1管和M2管的电流,所以由M1管和M2管构成的延迟单元处于电流饥饿状态。每一级迟单元处于电流饥饿状态。每一级的电流都由同一个电流源所镜像,所以Id1=Id2同时电流大小由输入控制电流Ictrl控制。

反相延迟主要是2个原因:一个是RC的充电时间;另一个是反相器的预置电压。而这2个延迟时间的产生都是可以通过调整宽长比来实现。环形反相的次数必须是奇数,这样电路才不会锁定导致振荡失败。而差动结构的振荡器级电路数可以是偶数,只要将其中的一级接成不反相的。这种灵活性是差动电路优于单端电路的一个优点。

摘要:研究了一种基于以太网物理层时钟同步的高带宽低噪声压控振荡器(VCO),该VCO采用交叉耦合的电流饥饿型环形振荡器,通过级联11级环路电路和改善其控制电压变换电路,优化了VCO的输出频率范围以及降低了输出时钟的相位噪声,完全满足以太网物理层芯片时钟电路的性能指标。基于TSMC 3.3 V 0.25 μm CMOS工艺的仿真结果表明,中心频率为250 MHz时,压控增益为300 MHz/V,其线性区覆盖范围是60~480 MHz,在偏离中心频率600 kHz处的相位噪声为-108 dBc。

关键词:VCO;环形振荡器;电流饥饿型;时钟同步

0 引言

在以太网中,物理层芯片(Physical Layer Interface Devices,PHY)是将各网元连接到物理介质上的关键部件。负责完成互连参考模型(OSI)第I层中的功能,即为链路层实体之间进行位传输提供物理连接所需的机械、电气、光电转换和规程手段。其功能包括建立、维护和拆除物理电路,实现物理层比特(bit)流的透明传输等。物理层包括4个功能层和两个上层接口。两个上层接口为物理介质无关层接口(MII)和物理介质相关层接口(MDI),在MII的上层是逻辑数据链路层(DLL),而MDI的下层则直接与传输介质相连。而这些子层的正常工作都离不开一个稳定精确的时钟同步信号。PLL在物理层芯片的时钟同步应用中,要求其输出时钟带宽覆盖范围广,电压控制频率线性度好,频谱纯度高。在PLL设计过程中,VCO是最为关键的设计环节,其性能将直接决定PLL的设计工作质量。近年来,VCO相位噪声得到越来越深入的研究,各种低噪声VCO结构不断涌现,文献中提到的交叉耦合电流饥饿型VCO便是其中一种。电流饥饿是指电路单元的电流受到电流源的钳制而不能达到其应有的最大值。本文在其基础上采用了一种有效控制电压变换电路,保证原有电路优点的同时扩展了线性度,提高抗噪声能力,有效降低了相位噪声。

1 VCO延迟单元工作原理

图1所示为电流饥饿型VCO中的单级结构。PNP管M1和NPN管M2是延迟单元的组成部分,Ictrl是用于控制电容的放电电流Id1和充电电流Id2,他们是构成环形振荡器的每一级。Ictrl控制着流过M1管和M2管的电流,所以由M1管和M2管构成的延迟单元处于电流饥饿状态。每一级迟单元处于电流饥饿状态。每一级的电流都由同一个电流源所镜像,所以Id1=Id2同时电流大小由输入控制电流Ictrl控制。

- 可靠和易用的 LTPoE++ 标准将 PoE 功率扩展至 90W(11-08)

- 高效的以太网供电解决方案降低了总体成本(06-07)

- 以太网供电应用中可用设备功率的估算(10-19)

- Xilinx Virtex UltraScale 开发平台(06-12)

- 基于以太网的可视对讲系统应用(08-30)

- 以太网在雷击浪涌测试中的应用(08-27)