利用FPGA实现无线分布式采集系统设计

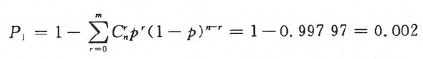

到现在为止,待发数据bit数为:208×2+8×2-432 bits。经调制解调后,接收端检测帧同步信息,同步信息为2组11100100组成。每组同步信息高7位与7位巴克码相比,允许出错位数在1位以内。设P为码元错误概率,行为同步码组的码元数,m为判决其允许码组中的错误码元最大数,在本系统中行n=7,m=1。在P=0.01时,单一barker码的漏同步概率为:

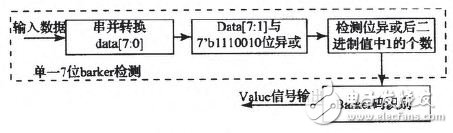

当2组同步帧都满足时,帧同步建立,接收端保 存接下来的数据。无线通信电台与FPGA以rs485连接,如图7所示,FPGA检测X是否为"0",当检测到"0",不接收端对接下来的数据X与本地巴克码对应位进行位异或运算。当检测1 byte barker码,错1位以内时,发出一value脉冲。当检测到2个value脉冲时,说明同步已建立,接收端开始存储接下来的数据。

图7 barler码识别

4 系统监控模块的实现

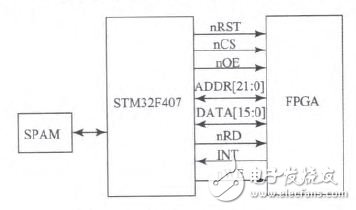

STM32与FPGA连接如图8所示,由于ARM与FPGA的相互通信直接影响着控制器的性能,所以该并行总线的设计就成为一个非常关键的问题。该总线可以包括芯片的地址总线(ADDR[021])、数据总线(DB[015])、控制总线、复位信号(nRST)以及中断信号线(INT),其中控制总线包括使能信号(nOE)、片选信号(nCS)、读信号(nRD)、写信号(nWE),这样做的好处是,将FPGA芯片存储器化,即STM32可通过对特定地址的访问来控制FPGA工作,并且可通过共同的复位信号将STM32与FPGA芯片同时复位,尽量避免总线竞争和冒险现象的出现。

图8 STM32与FPGA连接

STM32与FPGA同时接收命令,在解析完命令后,FPGA应在规定的时间内发送数据,FH认组帧完成时,发出INT信号至黜2申请中断。如果STM32在规定时间内没有接收到FPGA发来的INT信号,将开始计时,计时时间内未能接收INT信号,STM32将停止FPGA供电电源工作,由STM32代替FPGA工作,保证整个系统能稳定进行。

5 系统测试

编码器实物如图9所示。测试时搭建一对编码、译码器,采用12 V的直流电源供电。待 发数据为208 bits,即208‘b00000000_10010010_01100100_10011001_00100110_01001001_10010010_01100100_10011001_00100110_01001001_10010010_01100100_10011001_00100110_01001001_10010010_01100100_10011001_00100110_01001001_10010010_01100100_10011001_00100111_00111111;图10显示了测试中利用SignalTap II截取经卷积编码后输出的部分信号波形。其中z为串行输人数据,yt为卷积编码后输出的数据。数据经无线发送后,经Viterbi译码,仿真图形如图11所示,编码器发送的数据为208 bit S,data_out为译码输出的部分数据,译码数据与发送端的高低位顺序相反。由于数据经发送后,高低位互换,图上只截取了经Viterbi译码后的高27位的译码结果。经多次测试,数据传输正常,在少量不连续的错码情况下,系统能够自动纠正。

图9 编码器实物

图l0(2,1,4)编码器输出

图ll Viterbi译码输出

6 结论

在无线分布式采集系统设计中,采用了基于卷积编码、Viterbi译码的编码和互为备份的双通道传输方案,利用了FPGA内丰富的逻辑资源以及存储资源,实现了数据的远距离同步可靠传输。加入备份数据通道后,通过FPGA内部逻辑控制,在硬件上实现了对两路数据的实时校验及自动判选,提高了系统的稳定性和可靠性。相比于"备份-重传"等机制,该方法实现简单、实时性好,即使某一通道不能正常工作,系统仍能正常进行。该无线分布采集系统,满足了现在同步触发和数据量不大情况下的传输。本文提出的互为备份的双通道编解码、数据冗余传输机制,亦可应用相关无线传输领域,以提高远距离数据传输的可靠性和稳定性。

FPGA 相关文章:

- 用大电流LDO为FPGA供电需要低噪声、低压差和快速瞬态响应(08-17)

- 基于FPGA 的谐波电压源离散域建模与仿真(01-30)

- 基于FPGA的VRLA蓄电池测试系统设计(06-08)

- 降低从中间总线电压直接为低电压处理器和FPGA供电的风险(10-12)

- FPGA和功能强大的DSP的运动控制卡设计(03-27)

- DE0-Nano-SoC 套件 / Atlas-SoC 套件(10-30)