利用FPGA实现无线分布式采集系统设计

各译码器分时接收数据上传命令并上传数据-编码器将数据汇总保存至DDR2-数据收集齐后通过USB/RS485上传至上位机。译码器节点配合计算机对各个点的数据进行轮询采集,它包含了无线传输模块和与计算机通信的USB接口。STM32将组帧后的数据备份并实时监控FPGA,如在规定时间或未能按指令进行工作,STM32将替代FPGA并使FPGA进入断电状态。

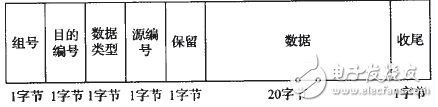

2.3 系统组帧格式

编码器与译码器之间是一对多的关系,译码器分时上传数据,译码器有2个通道,译码器有唯一的配置编号。数据帧的格式如图3所示。数据帧中除20字节有效数据之外,还包括组号、目的编号等。

图3 编码器、译码器间数据帧格式

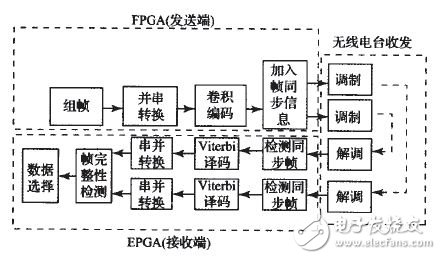

为了改进接收信号质量,本系统引入信道编码的方法来改善信道质量。具体如图4所示。发送端对数据进行组帧、并串转换、卷积编码、加入同步帧信息后,把数据发送至无线通信电台进行调制。接收端的无线通信电台对信号进行解调后发送数据至接收端的FPGA.接收端的FPGA检测到帧同步信息后对接下来的数据保存,并进行Viterbi译码。FPGA对双通道的数据进行冗余校验,并选择正确的数据执行相关操作。

图4 无线数据传输

3 无线分布式采集系统数据传输的实现

3.1 可靠性

待发数据经卷积编码,互为备份的双通道发送,Viterbi译码,冗余校验,数据判选,系统能够很好的进行无线收发。

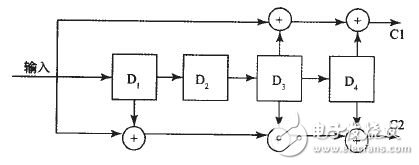

3.1.1 卷积编码

数据组帧完成后,由低位至高位进行并串转换,进行卷积编码。卷积编码是一种纠错信道编码,是由连续的输入信息序列经编码后得到连续输出的编码序列口。以(n,k,m)来描述卷积码,k为每次输入到卷积编码器的bit数,行为每k元组码字对应的卷积码输出n元组码字,m为编码储存度。卷积编码生成的n元组元不仅与当前输入有关系,还与前面m一1个输入的k元组有关系。本系统采用(2,1,4)卷积编码器,如图5所示。图中"+"代表异或。每bit经编码后都有2 bit输出(C1,C2)。

图5 (2,1,4)卷积编码器

3.1.2 Viterbi译码

接收端有2个接收通道,互不干扰。接收端对2个通道同时译码。译码采用Viterbi译码。Viterbi译码算法是一种卷积码的解码算法。Viterbi译码根据最大似然算法规则,能达到最佳译码,特别适合向前纠错。以本设计为例,根据图5,编码器4个延时状态(0,1)组成整个编码器的16个状态(D4D3D2D1),每个状态在编码器输入1或0时,跳转到另一个状态。并且输出也随之改变。译码就是编码的逆过程。算法规定任意t时刻收到的数据都要进行32次路径值计算、16次比较,比较后每个状态只保存一个路径值,为接下来计算减少了一半的运算量。反复208次,从16条幸存路径中选出一条路径值最小的,反推出这条路径,得出相应的译码输出。考虑到每次译码后,译码器都能回到初始状态,所以源数据最后加了8 bit的"0"。本设计采用并行处理结构,经214个周期还原出源码。

在设计FPGA逻辑时,基本采用多条并行的流水线技术,译码部分包含4个子模块:加比选模块、回溯模块、存储模块和时钟控制模块。路径值的计算和比较在3个时钟周期内完成,4个模块同时运行,大大的降低了译码时间。另外,为了提高FPGA效率,系统加入采样触发信号,保证系逻辑能够稳定运行。

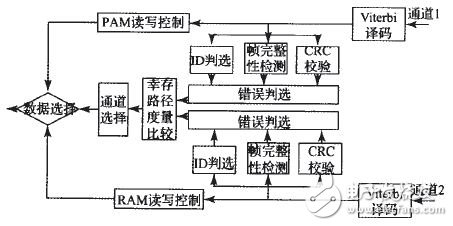

3.1.3 数据判选

经译码后,接收端已接收到2组互为备份的数据。经实践证明,简单的并联冗余能大大的提高系统的可靠性。具体选择流程如图6所示。2路数据经Viterbi译码后,开始接收一帧数据,并写入RAM中,同时计算CRC校验、帧完整性检测、ID是否符合本地。上述检测都没问题时,对2路幸存路径的度量值进行比较,选择值小的通道作为最终数据。

图6 数据的选择

3.2 同步的实现

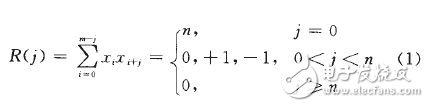

为了保证编码器和译码器之间能严格实现同步,数据帧需要加入同步帧。实现帧同步的方法通常有2种:起止同步法和集中式插入同步法。起止式同步比较简单,一般在数据码元的开始和结束位置加入特定的起始和停止脉冲来表示数据帧的开始和结束。集中插入式同步法中插人的同步码要求在接收端进行同步识别时出现伪同步的概率尽可能低,并且要求该码具有尖锐的自相关特性以便识别。7位巴克码作为帧同步码,其局部自相关函数为:

由上公式计算可知,7位巴克码的自相关函数在j一0时出现尖锐的单峰特性。设计中采用2组同步帧头作为同步码,同步帧头由7位巴克码和1 bit的0组成。

到现在为止,待发数据bit数为:208×2+8×2-432 bits。经调制解调后,接收端检测帧同步信息,同步信息为2组11100100组成。每组同步信息高7位与7位巴克码相比,允许出错位数在

FPGA 相关文章:

- 用大电流LDO为FPGA供电需要低噪声、低压差和快速瞬态响应(08-17)

- 基于FPGA 的谐波电压源离散域建模与仿真(01-30)

- 基于FPGA的VRLA蓄电池测试系统设计(06-08)

- 降低从中间总线电压直接为低电压处理器和FPGA供电的风险(10-12)

- FPGA和功能强大的DSP的运动控制卡设计(03-27)

- DE0-Nano-SoC 套件 / Atlas-SoC 套件(10-30)