利用FPGA实现无线分布式采集系统设计

1 引言

近些年来,随着电子技术的发展,无线通信技术、计算机网络的发展,分布式无线数据采集网络技术开始兴起,并迅速的应用到各个领域。在一些地形复杂,不适合人类出现的区域需要进行数据采集的情况下,都可以适当的选择无线分布式采集来进行。现有的无线分布式采集系统中,往往使用单片机、DSP等作为系统的主控控制单元。但是由于其自身工作特点,往往对于精确的定时控制以及并行处理能力上比FPGA弱。随着FPGA等可编程逻辑器件的发展,为无线数据可靠传输提供了很好的实现平台。采用FPGA作为时序控制和信号处理的处理器,将使系统电路设计更加简洁、可靠、灵活,可有效的缩短开发周期,并降低开发成本。

为此,基于CycloneIV+STM32设计了一种新型的无线分布式采集系统,实现了数据的高可靠和同步传输。设计主要由3大部分组成:编码器、译码器、无线收发电台。在对编码器、译码器同步校准后,对待发送数据进行卷积编码,并转换为串行数据。数据转换为串行数据后,在串行数据帧头加入Barker码来实现帧的同步,并使用2条互为备份的数据传送通道同时发送数据。在数据接收端检测到barker码后,本地对互为备份的双通道数据进行viterbi译码(本文设计的viterbi译码器采用并行结构,大大的降低译码时间)。译码结束后,本地对双通道数据进行循环冗余校验,并做出判选,最后执行相应指令。并在规定时间给出相应反馈信号。设计的无线采集系统,即使某一数据通道出现少量错码,系统仍能有效的恢复出数据,并进行可靠的数据传输。系统添加了监控模块,实时备份上传的数据并监控,如发现不能正常上传,则启用备用模块保证整个系统正常工作。系统不仅能实现数据的高可靠和同步传输,而且具有很好的适用性,可广泛应用工业中。

2 无线分布式采集系统简介

2.1 系统硬件简介

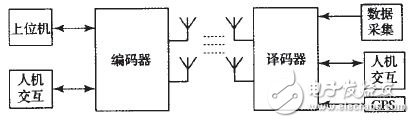

无线分布式采集系统包括编码器、译码器(编码器、译码器硬件完全相同,只是配置逻辑不同,可配置为编码器、译码器、中继站)和无线通信电台。如图1所示,这是一个最简单的一对一式分布式系统。

图1 无线分布式采集系统结构

编码器作为上位机与译码器之间的桥梁,通过USB/RS485通道进行发送、接收命令和数据。译码器接收编码器发来的命令进行配置和采集,并将数据存储至DDR2中。译码器收到上传命令后,上传数据至编码器。

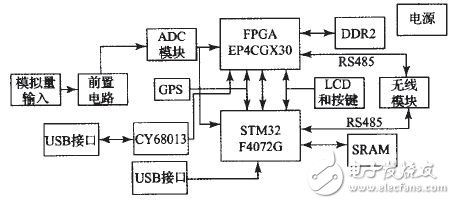

编码器/译码器硬件系统框图如图2所示。本系统主控单元由FPGA完成。FPGA选用Altera公司的EP4CGX30F407,逻辑单元为29440个,80个18×18乘法器,多达290个用户自定义IO。STM32作为监控和备用单元组成系统的基本架构,STM32F407ZG系列是基于高性能的ARM CortexTM-M4F的32位RISC内核,工作频率高达168 MHz,该STM32F407ZG系列采用高速嵌入式存储器(多达1 MB闪存,高达192 KB的SRAM),拥有3个12位ADC,2个DAC,1个低功耗RTC,12个通用16位定时器,2个通用32位定时器。人机交互部分由16X2液晶显示字符模块和4个按键组成,其主要功能是通过按键对基站编号设置并显示在LCD上。无线模块选用WSN-03系列无线模块作为收发平台,工作电压为5 V,传输速率和工作频段等都可配置。目前传输速率最大为115 200b ps,工作频为433 MHz可调。无线模块与FPGA主要以RXD/A,TXD/B,NRST(复位控制),SET(设置模块参数),SLP(休眠控制)信号线连接。GPS模块选用VKl6U6进行定位,与FPGA以UART接口连接,波特率定位9600 bps。ADC选用基于△-Σ技术的32 bits高精度低功耗模数转换芯片ADSl282,采样信号电平范围:差分输人一2.5~+2.5 V。单个译码器有6个采集通道,以2 k采样率,采样时常16 S来计算,单个译码器纯数据量为6×2 k×16×24-6144 Kbits.考虑到编码器,一次采样,8个基站的数据经编码后数据总量为98 304 Kbits,所以编码器和译码器需增加l片Micron Technology公司的MT47H256M8HG-37E IT(256Meg×8)作为缓存空间。由于DDR2 SDRAM需要特定的控制读写时序,系统直接采用Quartus II自带的"DDR2 SDRAM High-Performance Controller"IP CORE。USB部分由2个通道组成,一个是由FPGA、CY7C68013和USB接口组成;另一个由STM32(自带USB驱动)和USB接口组成。同时本设计中还添加了RS485串口,使整个系统与上位机能保持实时通信,为系统的远程控制提供了可能,并能保持系统更新。

图2 系统框架

2.2 系统数据流程

系统的数据流程为:同步校准译码器,设置各个译码器接收命令后的延时-编码器配置采集参数、命令-译码器采集数据保存至DDR2中一

FPGA 相关文章:

- 用大电流LDO为FPGA供电需要低噪声、低压差和快速瞬态响应(08-17)

- 基于FPGA 的谐波电压源离散域建模与仿真(01-30)

- 基于FPGA的VRLA蓄电池测试系统设计(06-08)

- 降低从中间总线电压直接为低电压处理器和FPGA供电的风险(10-12)

- FPGA和功能强大的DSP的运动控制卡设计(03-27)

- DE0-Nano-SoC 套件 / Atlas-SoC 套件(10-30)