基于FPGA的雷达回波实时模拟器的实现

时间:07-10

来源:互联网

点击:

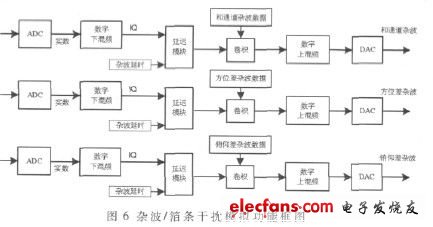

生高斯白噪声随机序列,FFT后根据噪声带宽进行加窗,得到噪声序列的频谱,然后做IFFT,得到时域模板序列。对这个模板序列进行随机移位叠加,最后根据测频结果进行DUC,将噪声移到一定的载频上。根据实际噪声带宽的需求,可以选择不同宽度的窗函数,控制调频噪声的带宽。

将上述运算过程生成的目标回波、噪声、杂波和干扰信号叠加后,即可得到最终的雷达回波信号。

3 系统验证

分别采用连续波信号和脉冲信号对系统的功能和性能进行测试。连续波状态下,需要测试模拟器的输出功率、杂散抑制、动态范围、多普勒信号控制性能等指标。脉冲状态下,需要测试模拟器的模拟精度、多目标及干扰模拟能力等指标。

图7给出了连续波状态下某典型频率的输出信号实测结果。可以看出,输出点频信号的频率与输入信号相差所设定的多普勒频率,杂散电平很低,满足一般雷达系统的要求。表1给出了主要指标的实测结果,包括输出功率、、杂散抑制、输出动态范围、多普勒信号频率范围与多普勒频率精度等。

图8给出了脉冲状态下的输出信号,表2给出了主要指标的实测结果。

本文介绍了一种基于FPGA嵌入式系统的雷达回波实时模拟器。利用FPGA资源丰富、并行运算能力强的优点,提高了系统的集成度与实时性;采用System Generator开发FPGA软件,大大降低了开发难度与开发周期;通过灵活配置FPGA软件,可以实现不同体制雷达回波的模拟,具有较强的通用性和扩展性。实验结果表明,该模拟器能够满足雷达系统半实物仿真的需求,其相关技术代表了雷达回波模拟器未来发展的一个方向,并可应用于其他类型的回波模拟中。

- CPCI总线的分布式系统设计应用(06-02)

- 用大电流LDO为FPGA供电需要低噪声、低压差和快速瞬态响应(08-17)

- 基于FPGA 的谐波电压源离散域建模与仿真(01-30)

- 基于FPGA的VRLA蓄电池测试系统设计(06-08)

- 降低从中间总线电压直接为低电压处理器和FPGA供电的风险(10-12)

- FPGA和功能强大的DSP的运动控制卡设计(03-27)