基于FPGA的雷达回波实时模拟器的实现

雷达回波模拟器能够在实验室环境下模拟产生雷达实际工作中所接收到的回波信号,在雷达系统设计、调试、测试、训练和维护等工作中发挥着不可替代的作用[1-3]。随着电子技术的日益进步,雷达系统正在向多模式、多通道、高分辨等方向发展,对模拟器的通用性、实时性等指标提出了更高的要求[4]。

模拟器通常可以分为软件模拟、硬件模拟及软硬结合等三种实现方式。软件模拟具有成本低、灵活性强等优点,但实时性差,一般不能直接用于雷达系统的实时调试和测试[5]。硬件模拟通常采用波存储回放技术,实时性好,但通用性差,不能满足参数复杂多变的情况[6-7]。软硬结合方式以通用计算机为主控平台,以高性能嵌入式处理器为运算单元,在具有良好实时性的同时,能够适应复杂的仿真环境,是应用最为广泛的模拟方式[5,8]。

FPGA作为高性能数字信号处理系统中的关键器件,在雷达信号模拟中有着巨大的开发潜能[9-11]。然而,受制于开发难度与开发周期,在传统的模拟器中,FPGA多用于逻辑功能、时序信号和对外接口的控制,其强大的并行处理能力没有得到充分利用。

本文以FPGA为核心构建了一种通用的雷达回波信号实时模拟系统。该系统采用FPGA作为回波信号模拟的运算单元,充分利用了FPGA资源丰富、并行处理能力强的特点,提高了系统的实时性;采用System Generator开发回波模拟程序,大大降低了开发难度,并显着缩短了研制周期。采用标准工业总线及模块化设计,通用性、兼容性和可扩展性强,可以应用于不同体制、不同规模的雷达系统模拟中。

1 系统方案

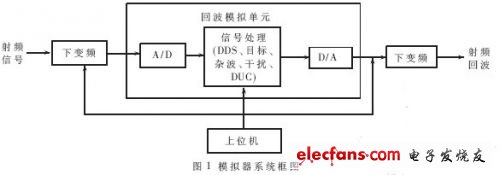

通用雷达回波实时模拟器(以下简称"模拟器")由上位机、微波链路和回波模拟单元组成,系统框图如图1所示。上位机实现人机交互、系统控制、状态监视等功能。微波链路包括下变频和上变频模块,用于实现射频信号与中频信号的转换。回波模拟单元完成中频信号采集、数字下变频(DDC)、目标模拟、杂波模拟、干扰模拟、数字上变频(DUC)和数模转换等操作,是整个系统的核心模块。

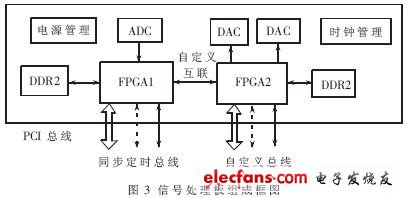

模拟器遵循标准结构规范,采用cPCI标准总线,可根据实际需求扩展系统规模,为工程应用提供了便利。为了适应不同速率、不同类型的信号传输,系统内部采用多种互联方式。PCI总线用于传输控制命令及慢速信号,自定义总线用于高速数据流的传输,同步定时总线用于系统的时序控制,如图2所示。

作为模拟器的重要组成部分,回波模拟单元以高性能FPGA为核心构建,用于实现DDC、回波模拟、DUC等功能;同时配以高速A/D和D/A芯片,用于信号采集与回波信号的播放。回波模拟单元由多块信号处理板组成,单板的逻辑框图如图3所示,FPGA采用2片Xilinx公司的XC6VLX240T。芯片采用40 nm技术,密度高、功耗小,片上具有丰富的逻辑和I/O资源,并集成了大量的信号处理单元(DSP48E),能够满足复杂的回波模拟运算及对外接口的需求。两片FPGA通过自定义互联接口实现高速数据通信,用于传输中间结果。ADC采用ADC08D1500,最高采样率可达1.5 GHz,可以满足中频宽带信号的采样要求。DAC采用ADI公司的AD9736,最高时钟频率为1.2 GHz,具有良好的输出信号性能。

2 FPGA模拟软件设计与实现

雷达回波信号是目标回波、杂波、干扰以及噪声等叠加后的结果。不同的雷达体制,对目标、杂波、噪声及干扰的建模方法有所不同。对于雷达导引头,可以仅考虑单点目标,只需模拟目标的速度、加速度、距离和功率等信息即可。对于复杂的高分辨雷达系统,则要求模拟器能够更为细致地模拟目标回波信号,如动目标、一维距离像及面目标等。

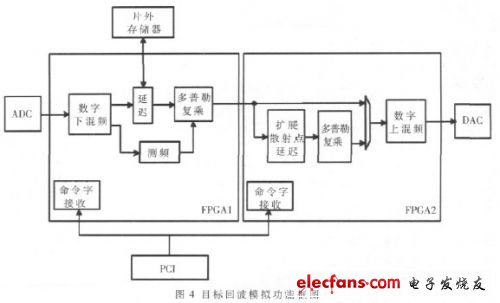

图4给出了目标回波模拟软件的功能框图。该软件可以模拟点目标以及扩展目标的回波信号。中频输入信号在完成DDC后作为回波模拟的基带基准数据,同时用于确定波门和载频。多普勒计算模块根据设定的目标运动信息及测频结果计算每个目标的多普勒频率。波门信息与目标延迟信息相结合,用于确定回波信号的位置。复乘模块在基准数据上加入延迟、多普勒调制和幅度调制后得到基带回波数据,再经过DUC后通过DAC播放,即可得到中频回波数据。

由于信号处理板卡具有2片FPGA,因此需要将上述各运算模块分别映射到相应的FPGA中。如图4所示,第一个FPGA实现数字下混频、测频、延迟复乘等功能,第二个FPGA实现扩展散射点延迟、各点相对多普勒复乘、数字上混频等功能,产生一个简单目标或一个扩展目标。为了降低开发难度、缩短开发周期,运算模块均采用System Generator开发。

噪声模拟的实现方法如图5所示。首先产

- CPCI总线的分布式系统设计应用(06-02)

- 用大电流LDO为FPGA供电需要低噪声、低压差和快速瞬态响应(08-17)

- 基于FPGA 的谐波电压源离散域建模与仿真(01-30)

- 基于FPGA的VRLA蓄电池测试系统设计(06-08)

- 降低从中间总线电压直接为低电压处理器和FPGA供电的风险(10-12)

- FPGA和功能强大的DSP的运动控制卡设计(03-27)