DC综合后的网表求解

时间:10-02

整理:3721RD

点击:

小弟的代码sigma.v由于有分频器,在综合之前手动加入了库里的buf单元:

BUFX4 U0 ( .A(ck), .Y(CK) );

BUFX4 U1 ( .A(ckb), .Y(CKB) );

在综合时脚本中加入了set_dont_touch {U0 U1},DC综合的结果并没有报告任何时序违例情况;综合之后导出网表sigma_dc.v,sigma_dc.sdf,进行仿真。

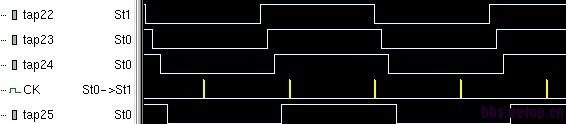

但是:①仿真的时候如果只加入sigma_dc.v的话,波形跟前仿真不一样,如下图,CK为输出波形,CK理应也是个占空比为50%的时钟波形。

②而在仿真网表sigma_dc.v时,在测试文件中加入延时文件sigma_dc.sdf后,仿真波形跟前仿真是一样的。

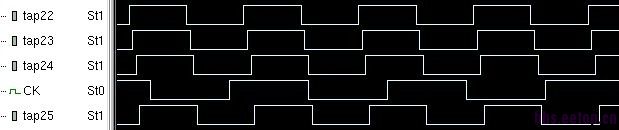

仿真波形如下图,此时波形是正确的:

请问:我这样的综合算是成功的吗?可以拿去做布局布线了吗?多谢指点。

1、不反标sdf的话了一个buf的延时就是1ns(timescale是1ns),10个串联BUF就是10,比如这10个BUF在两个DFF之间,DFF的clock period是5ns,这样的话一个周期下来,第一个DFF的Q端还不能传到第二个DFF的D端

在不反标sdf的时候把你的clock period加大,或者加选项只仿真function,加no specify选项什么的,一般STD cell veriog里会define FUNCTIONAL,在compileverilog的时候加上define FUNCTIONAL就OK了

另外综合的结果没必要加SDF仿真

你好,我有两条路径分别只插入1个buf,如果不加sdf文件仿真的话,波形不对。但加上sdf后,仿真波形是正确的。如果找您说的“另外综合的结果没必要加SDF仿真”,岂不是我的综合结果就是错的了?要重新综合?

我用的VCS脚本是:vcs -f sigma.f -v smic18.v -debug

另外:我综合的时候DC并没有报任何时序违例,但用PT分析的时候却有时序违例情况,setup,hold都有问题。但DC网表加sdf文件波形又是正确的,我接下来该如何是好呢?

请问一下,你这个问题之后是怎么解决的,我现在也遇到这个问题了

顶贴赚积分

dingyixia ~

学习了!