求clock_gating导致的保持时间违例的解决办法

本人使用的是0.35um的工艺库,为了降低动态功耗在DC阶段使用compile -gate_clock插入了门控时钟(库中没有集成型的,此门控时钟的锁存器和与门是分开的),在ICC阶段,执行完CTS后报告时序,结果如下:

min_delay/hold ('clk' group)

RequiredActual

EndpointPath DelayPath DelaySlack

----------------------------------------------------------------- -----------------------------

chip/M3/A2/clk_gate_dout_tem_reg/main_gate/A153.533.13 r-50.39(VIOLATED)

chip/clk_gate_ACRR_reg/main_gate/A153.242.98 r-50.26(VIOLATED)

chip/clk_gate_dataout_reg/main_gate/A153.242.98 r-50.26(VIOLATED)

chip/clk_gate_REGB_reg/main_gate/A153.202.98 r-50.22(VIOLATED)

chip/clk_gate_r_dor_reg/main_gate/A153.243.02 r-50.22(VIOLATED)

chip/clk_gate_wr_reg/main_gate/A153.243.05 r-50.18(VIOLATED)

chip/clk_gate_shift_reg_reg/main_gate/A153.203.04 r-50.16(VIOLATED)

chip/M8/clk_gate_out_temp_reg/main_gate/A153.183.14 r-50.04(VIOLATED)

chip/M8/clk_gate_FSR_reg/main_gate/A152.862.98 r-49.88(VIOLATED)

chip/M8/clk_gate_OCC_reg/main_gate/A152.832.98 r-49.85(VIOLATED)

chip/M8/clk_gate_den_temp_reg/main_gate/A152.863.06 r-49.81(VIOLATED)

chip/M8/clk_gate_num_temp_reg/main_gate/A152.833.08 r-49.76(VIOLATED)

chip/clk_gate_REG_reg/main_gate/A152.542.96 r-49.58(VIOLATED)

chip/M8/clk_gate_data_GCC_temp_reg/main_gate/A1 52.542.99 r-49.55(VIOLATED)

由上可知,门控时钟与门A1(与锁存器Q相连)存在很大的保持时间违例。目前尝试让锁存器跟与门尽量靠近,锁存器EN端尽量离各锁存器最近,且将它们固定,但是CTS后的违例依旧没有减小。问:在不插入大量缓冲器的情况下,如何减小这类保持时间违例?

顶顶顶

寄存器是上升沿触发的吧?可以贴个具体的timing path。

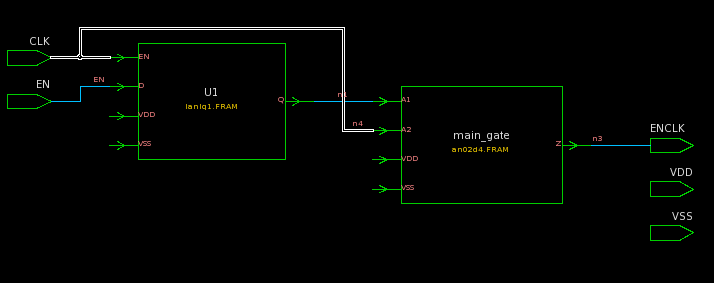

我找到的原因是A2与EN在CTS之后,A2端插入了好几个buffer,且两端口连在同一主时钟的不同支路上面。CTS前后连接关系分别如下图所示:

本人尝试过在CTS之前,将此clock_gate设置为dont_touch属性,但是CTS之后的结果仍旧一样。问:怎样才能使其CTS之后EN端仍和A2端相连?又或者,是否可以在布线之后手动更改网表使EN端直接与A2端连在一起?如果可以,又该使用何指令呢?

发现新问题:设计中有个名为POL的端口,在默认状态下,POL=1,所以在约束时使用set_case_analysis POL 1;当POL=0时,主时钟反相。在CTS之前执行remove_case_analysis -all ;CTS之后出现上述时序问题,此时我再set_case_analysis POL 1,则时序违例目前最大为0.74ns(复位路径上的) ; 再执行remove_case_analysis -all,再执行set_case_analysis POL 0,则没有时序违例了。上述两种情况都没有了clock_gate上的时序问题,问:这是什么原因造成的?

clk端口与clk_cts_5前面的支路是什么样的?对于你贴的那个图,我的理解是在EN端前面插一个inverter,让到EN端与到A2端的clock 信号反相,相当于寄存器用下降沿触发,这样hold好满足。同时对于你说的POL端case会影响时序结果,你得看具体的timing report找原因。