关于encounter中via12 与stdcell的blockage之间的drc问题

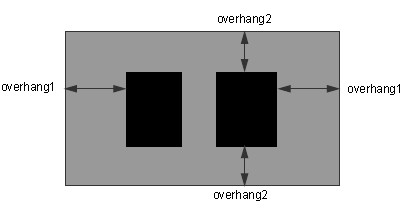

如图蓝色部分为stdcell的M1 blockage部分,黑色矩形框为lef文件中的V12的M1部分,紫色部分为drc报错部分。

当在stdcell的pin端打V12时会出现很多图中情况,V12的M1与stdcell的M1 blockage间距不满足要求,像这种情况如果选用M1和M2均为垂直方向的VIA12可以避免DRC报错,一般PR工具会自动选择合适的VIA12以避免DRC错,但是工具还是报了很多这样的错误,这个问题怎么解决?有什么优化via的方法吗?

补充下:在lef文件中存在M1和M2均为垂直方向的VIA12,正常情况下encounter会自动修正的,为什么还会出现这种情况?

偶记得 icc 有 advance via rule可以规定 1x2什么的, edi 目前不太清楚

印象中有设置,不让打孔在pin

你在lef中的V12 怎么定义的?

主要还有很多不是直接打在pin上的。

VIA VIA12_H DEFAULT

RESISTANCE12.000000000 ;

LAYER M1 ;

RECT -0.240 -0.240 0.240 0.240

LAYER MV1 ;

RECT -0.140 -0.140 0.140 0.140

LAYER M2 ;

RECT -0.240 -0.240 0.240 0.240

END VIA12_H

诸如此类有6种。其他的包括:HH , HV ,VH ,VV 等类型(图中的为HV型的即M1横向长,M2纵向长)

嘻嘻,谢谢。

还有个地方 你看下,尺寸如何。如下:VIARULA V12GENERATE

LAYER M1

DIRECTION ****

OVERHANG ***

METALOVERHANG ****

*

*

*

END V12

参考 LEF/DEF 5.5 Language Reference 中定义

LAYER M1

TYPE ROUTING ;

DIRECTIONHORIZONTAL ;

OFFSET0.280 ;

PITCH0.560 ;

WIDTH0.280 ;

SPACING0.280 ;

AREA0.360 ;

THICKNESS0.525 ;

HEIGHT0.9845 ;

MINIMUMEDNSITY30 ;

SPACING0.560RANGE10.001 10000.0 ;

RESISTANCE RPERSQ0.1250000000;

ANTENNACUMSIDEAREARATIO600 ;

DCCURRENTDENSITY AVERAGE 1 ;

END M1

M2 与M1 除了thickness和height不一样,其他都一样

LAYER MV1

TYPE CUT ;

SPACING0.280 ;

ANTENNACUMAREARATIO20 ;

ANTENNACUMDIFFAREARATIO PWL ........

ENDMV1

之前我说的那个HV型的via1如下:

VIA VIA12_HV DEFAULT

RESISTANCE12.000000000 ;

LAYER M1 ;

RECT -0.280 -0.140 0.280 0.140 ;

LAYER MV1 ;

RECT -0.140 -0.140 0.140 0.140 ;

LAYER M2 ;

RECT -0.140 -0.240 0.140 0.240 ;

END VIA12_HV

overhand1 = 0;

overhand2 = 0.14;

Nanoroute的mode中AdvDRC, 选上 enclouse via ... in stdcell pin,再试试,有惊喜。

大神,是惊喜,问题解决了,非常感谢。

eetop果然是个好地方啊,哈哈