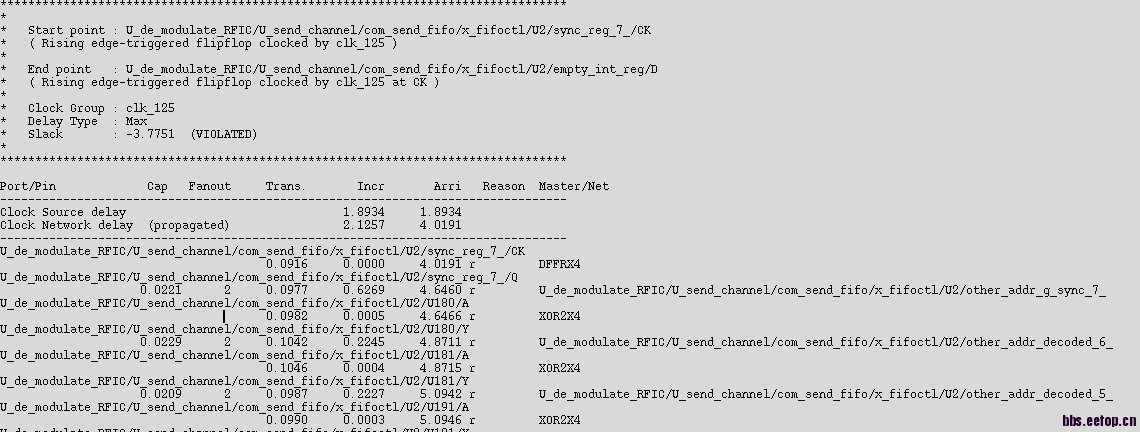

Clock Network delay (propagated)

两者的区别?

看不清你的log!

说变描述一下,

clock source delay:约束的是输入时钟到你startpoint之间的延时。

Clock Network delay:clkin 到clkout之间"clock source delay+ clock 走过的buffer"

多多交流!

不对,

clock source delay 是到你定义的时钟的那个端口之前的时钟延迟,或者说源时钟本身的延迟

确切地英文解释为“Clock source latency is the time it takes for a clock signal to propagate from its actual ideal waveform origin point to the clock definition point in the design. ”

如果不涉及几个源时钟之间的关系,一般不用定义source delay

clock network latency 是从你定义的时钟的那个端口之后,到FF之间的延迟,也叫clock inserion delay

陈老大, 模拟一下实际clock有可能在源端产生的delay, 定义一下也是可以吧?

可以是可以,可是没有必要

thanks for sharing

its good

涛哥

我在手册上看到Source latency, also known as insertion delay, is the time it

takes for a clock to be propagated from its ideal waveform origin point to the clock definition

point in the design.

那clock insertion delay也就是insertion delay的一部分啦?

版大,如果clk_a是create clock,clk_b是clk_a的generated_clock,那么在dc综合的时候对clk_a如果设置set_clock_latency-source la1 [get_clocks clkb]

set_clock_latencyla2 [get_clocks clka],

那么如果我想设从clk_a的定义点到clk_b的定义点的时间为la3,我用命令

set_clock_latency -source la1+la2+la3 [get_clocks clk_b]对不对?

还是直接设置为set_clock_latency -source la3 [get_clocks clk_b]?

thanks for sharing