请教STA中set_output_delay -min 对保持时间做约束时间为什么可以为负值呢?

setup能理解 hold怎么不理解呢

hold是希望data 上的path的延时足够大,如果设了负值。那么工具至少都会去插1.5的延时 去fix这个-1.5.

我说明白了吗?

没有说明白

set_output_delay的意思是外部virtual logic部分的延迟

-min的意思是那部分的最小延迟

如果要求clkp后输出继续保持1.5ns,就是说外部缺1.5ns

所以-min -1.5

谢谢回复,那请问clkp后输出继续保持1.5ns,是指DUA内部数据通过组合逻辑传播到QOUT的延时应该是1.5ns吧,与外部的逻辑有啥关系呢?

假设外部的逻辑,便于理解

当virtual logic capture时,其hold time 值也必须是正的,至少也得是0,

既然你设置了launch 寄存器的output delay 为负,那么

工具必须把从QOUT的virtual logic 的D端补上1.5ns的延时。

其实这么作,就是为了保证hold time 不出错。

夜深了,明天再看

谢谢回复,那是不是可以理解为如果DUA内部clk到QOUT的延时没有1.5ns,DC就会往这条路径加buf,使延时满足1.5ns吗?

是的,就是为了满足保持时间,不然新数据会冲掉外部那个触发器的输入信号

我认为是的

其实,从物理上讲,launch reg的 Q输出端的输出延时不可能是负的,一定会大于0,但是可能不到1.5ns,

所以,你可以骗工具,说其输出端的输出延时是负的,工具就会帮你补上1.5ns,

有了这1.5ns的延时,再加上launch reg 的clk -> q 的本征延时,那virtual reg 的hold 一定没问题了

小编看的是什么书?求推荐

这篇帖子要在前端版块就好了

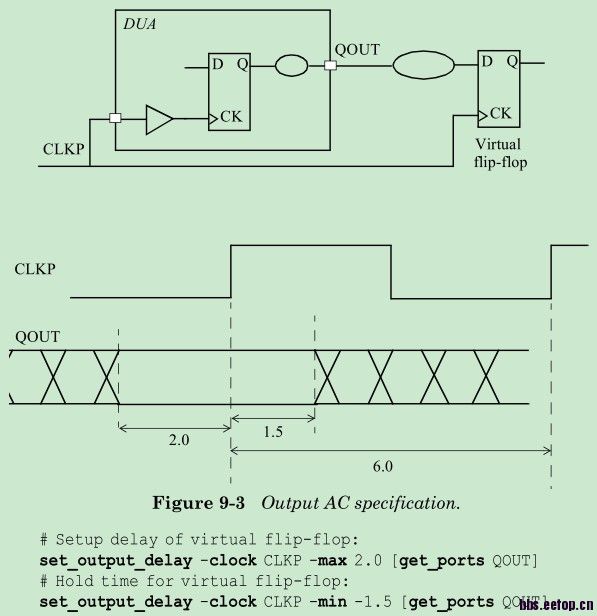

我看的<Static Timing Analysis for Nanometer Designs>,J. Bhasker•Rakesh Chadha写的,和小编约束的不一样,他是这么约束的:

create_clock xxxxxxxx (声明随路时钟,虚拟时钟,声明在output pin上)

set_output_delay -max -1.5 -clock xxxxx

set_output_delay -min 2.0-clock xxxxx

我的理解应该是按照小编的约束才对,即-max 2.0,-min 1.5,但是我看的这本STA书上是完全相反的。

对于负值的解释,书上也很笼统,“Notice that themin value of the output delay specification is larger than the

max specification. This anomaly exists because, in this scenario, the output

delay specification does not correspond to an actual logic block. Unlike the

case of a typical output interface where the output delay specification cor-responds to a logic block at the output, the set_output_delay specification in

a source synchronous interface is just a mechanism to verify whether the

outputs are constrained to switch within a specified window around the

clock. Thus, we have the anomaly of the min output delay specification be-ing larger than the max output delay specification.”

有这本事的,你们参考一下9.1.3节,看我理解的对不对。

set_output_delay -max 是指虚拟的组合逻辑,加上虚拟flip-flop的setup时间的最大值。因为图中已说明QOUT会在时钟上升沿2ns之前达到稳定,那么只要满足外部虚拟组合逻辑+时序逻辑的最大延时不超过2ns就可以让虚拟flip-flop正确采样。同理,set_output_delay -min 是指外部虚拟组合逻辑加上虚拟flip-flop的hold的最小时间,因为图中QOUT会在时钟上升沿后1.5ns保持稳定,因此,即使外部虚拟逻辑的值为负值,依然可以保证虚拟flip-flop正确采样,最小负值为-1.5ns。

看了这么多答案,终于理解了这个问题。虽然时间有点远但还是很有帮助,顶

我认为这里应该有一个电路环境在:

virtual ff的时钟相对于CLKP是有一定延迟的,或者说CLP要输出至板级的某个sram等模块,在这段路径中就产生了相应的时钟延迟,为了保证hold不违例,即launch ff发出的数据的时钟沿,与capture ff捕获该数据的时钟沿不是相同的沿,故在数据路径上增加一个min delay,以补偿virtual FF的clock延迟,保证数据不被覆盖。