时序约束问题求教

create_clock-name clock -period 10 [get_pinsU145/A]

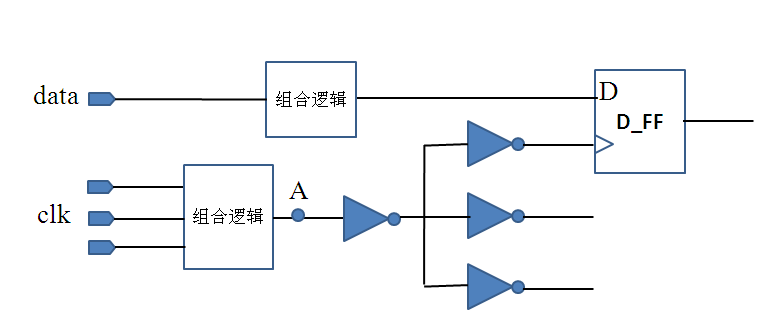

为了方便对input_delay进行准确设置,我想知道从时钟输入端口clk到点A之间的这段组合路径的延时,于是我对这条路径设置如下约束:

set_max_delay1.5 -from [get_portsclk] -to [get_pinsU145/A]

set_min_delay0.5 -from [get_portsclk] -to [get_pinsU145/A]

然后对这条路径进行时序分析。可是当我用如下命令对这条路径报告时序的时候,Encounter告诉我没有这样的路径或者说没有约束,怎么回事?我应该怎么设置约束?实际上我也知道它不属于我们常说的四种基本时序路径,那我怎么来获得它的延时呢?

report_timing -from [get_portsclk] -to [get_pinsU145/A]

如果是DC可以考虑以下命令:

check_timing

report_port

report_timing_requirements

report_clock

report_transitive_fanin

report_disable_timing

report_lib -timing_arcs

如果是PT可以考虑:

report_analysis_coverage -status_details untested

check_timing -verbose

report_exceptions

report_timing -exceptions all

供参考

谢谢您的热心解答,您提供的这些命令似乎都是查看端口有没有约束或者说我上面说的所谓的路径有没有约束。这个确实没有约束,我想请问这样的“路径”该怎么约束呢?或者怎么获得它的延时呢?谢谢

虽然不明白你在做什么,我只能告诉你 ICC 的话有 report_delay_calculation, Encounter 就不清楚了。

我觉得你未必很清楚什么是 input delay, set_max_delay, set_min_delay, report_timing

只要从 clk 端口到 U145/A 有实际的物理路径,就能报出delay。

时序约束只留下这两句试试,其他什么约束都不要加,包括 create_clock都不要。

set_max_delay1.5 -from [get_portsclk] -to [get_pinsU145/A]//这句就是对想check的路径设置的约束。report_timing -from [get_portsclk] -to [get_pinsU145/A]

如果这样执行出来的结果还是说 unconstrained,说明 set_max_delay 这句约束失效。然后重新考虑 起始点 和 终点的设置。

我这么说你看对么?

input_delay + 数据从input port 到reg之间的组合路径上的延时 + setup <= a clock cycle. 那么input_delay自然就是数据从上一级传到input_port这之间的外部延时。set_max_delay相当于是约束路径上的延迟值不能超过这个规定的值,当然如果路径起点有input_delay的时候,它会把这个值算进来,对于终点如果有output_delay的时候,它也会把这个值算进来。set_min_delay那就可想而知是约束路径最小延时的了。对于report_timing,它的选项太多,功能也就很多了,就不一一列举。不过一般用的多的是报告路径延时,时序计算。

我上面说的如果有不准确的地方请多指正。

我为什么在上面的问题中问从clk到A点的延时呢?因为这个延时本来应该是属于clock latency的不?clock latency对于从input port到FF路径的setup是有利的,但是对于hold确是不利的,我想把clock latency考虑进来。然而,由于我把时钟节点定义在A点,那么工具计算clock latency的时候,只会计算从A点到触发器这段延时不?那么从输入端clk到A点的这段延时呢?说白了我想知道这段延时是多少?

然而从输入端clk到A点又不属于我们所说的四种基本时序路径之一,所以我认为我上面写的那个约束set_max_delay -from [get_ports clk]

-to [get_pins U145/Y] 根本就没用,因为工具不会认为这是一条时序路径啊。该怎么来知道它的延时呢?请赐教!

我试试,谢谢您的帮助,一会看看结果。

icc 中应该可以这样得到

report_delay_calculation

report_clock_timing

不知道你这样设的用处

可否考虑这样设

create_clock-name CLK-period10 [get_ports clk] -wave {0 5}

create_generated_clock-name clock[get_pinsU145/A] -source[get_ports clk]-master_clock[get_clock CLK ] -divide_by 1 -add

正解!

谢谢您的热情帮助,受教!

按你说的,只加那一句约束,不加别的,可以报告出来,那可能就是我的时序约束中别的约束把这个覆盖了

谢谢您的热情指导!

“ 可否考虑这样设

create_clock-name CLK-period10 [get_ports clk] -wave {0 5}

create_generated_clock-name clock[get_pinsU145/A] -source[get_ports clk]-master_clock[get_clock CLK ] -divide_by 1 -add ”

弱弱地问一句,这样设置后,input_delay应该是相对于这个生成的时钟clock设置还是相对于源时钟CLK设置呢?工具在计算clock latency的时候,只会计算从A点到FF之间的延时吧,不会考虑从源时钟到生成时钟之间组合路径的延时对吗?

是不是因为A节点被定义为时钟,所以在用report_timing -from -to的时候,被认为从输入port clk到时钟clk驱动的寄存器输入端 不存在路径?

是不是这个原因可以使用如下方法判定:

set_max_delay1.5 -from [get_portsclk] -to [get_pinsU145/I2]

set_min_delay0.5 -from [get_portsclk] -to [get_pinsU145/I2]

report_timing -from [get_portsclk] -to [get_pinsU145/I2]

学习了

markyixia

首先有点疑问?是否propagated 后报的delay?

其次encourage中report_timing 应该是报不出来,这个只能报出四种path的timing。

可以通过help 命令help ×del× 来查看关于计算delay的命令,还可以用report_timing_arc 命令报这个cell的delay也能得到一个大概值。手头没有服务器,只能给你说个想法,明天帮你测试下再看看。

同样初学,互相学习