PT transitition

时间:10-02

整理:3721RD

点击:

刚开始看Primetime有很多问题想问一问大家

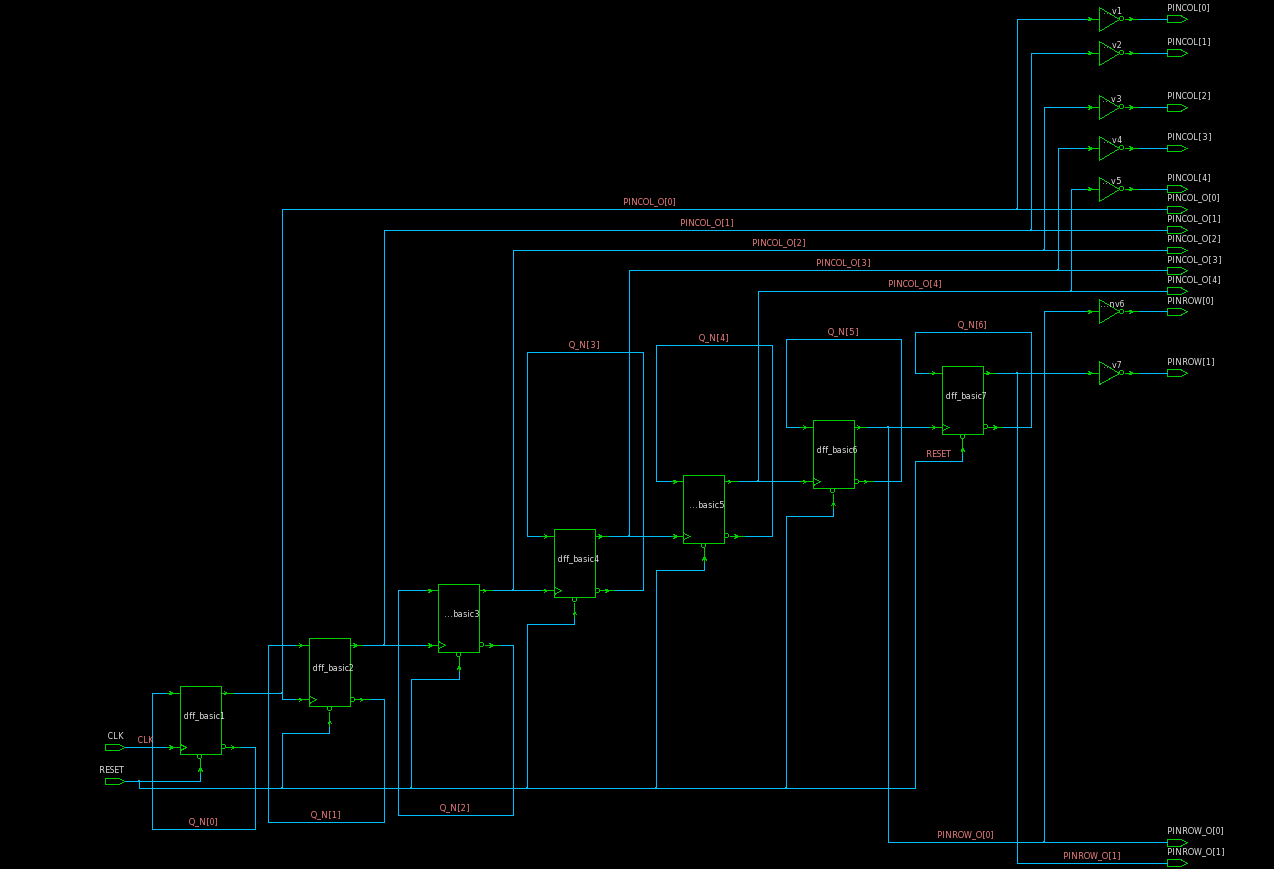

我在做一个7级DFF,主要目的是想看看他们的setup和hold,因为每一级transition的时间,想看看到了后面是否会出现IR drop之类的问题。

简单的电路图

问题大致有下面几个

第一,对于lib里,每个cell的port会有自己的表格,从而查出在不同电容的时候他对应的rise/fall transitiont时间。那我在实际设计的时候如果超出了这个范围那就是violation?其实我不太理解这个表格的意思。

第二,一开始设置一个最前端的clk,发现从第二级开始,每一级的CK输入都要设置一遍generated clk,结果如下

ClockPeriodWaveformAttrsSources

-------------------------------------------------------------------------------

CLK20.00{0 10}p{CLK}

CLK240.00{0 20}p, G{dff_basic1/Q}

CLK380.00{0 40}p, G{dff_basic2/Q}

CLK4160.00{0 80}p, G{dff_basic3/Q}

CLK5320.00{0 160}p, G{dff_basic4/Q}

CLK6640.00{0 320}p, G{dff_basic5/Q}

CLK71280.00{0 640}p, G{dff_basic6/Q}

GeneratedMasterGeneratedMasterWaveform

ClockSourceSourceClockModification

-------------------------------------------------------------------------------

CLK2CLKdff_basic1/QCLKdiv(2)

CLK3dff_basic1/Qdff_basic2/QCLK2div(2)

CLK4dff_basic2/Qdff_basic3/QCLK3div(2)

CLK5dff_basic3/Qdff_basic4/QCLK4div(2)

CLK6dff_basic4/Qdff_basic5/QCLK5div(2)

CLK7dff_basic5/Qdff_basic6/QCLK6div(2)

由于我最终的目的是想把每一级的clk transition time给遗传到下一级,看看最后他的transition time是否过大,但我在看每一级的setup和hold的时候永远都是每一级都是一样的,是不是我的generated clock产生的有问题?

第三,我用set_clock_transition这个命令去给clk加transition time,但不论我加不加所有的setup 和 hold都不会变化,是不是有其他的设置我没有开?

由于是第一次用,对于这些电路的概念很多也是临时补起来,难免有疏漏。如果有低级的错误还请指正啊!

我在做一个7级DFF,主要目的是想看看他们的setup和hold,因为每一级transition的时间,想看看到了后面是否会出现IR drop之类的问题。

简单的电路图

问题大致有下面几个

第一,对于lib里,每个cell的port会有自己的表格,从而查出在不同电容的时候他对应的rise/fall transitiont时间。那我在实际设计的时候如果超出了这个范围那就是violation?其实我不太理解这个表格的意思。

第二,一开始设置一个最前端的clk,发现从第二级开始,每一级的CK输入都要设置一遍generated clk,结果如下

ClockPeriodWaveformAttrsSources

-------------------------------------------------------------------------------

CLK20.00{0 10}p{CLK}

CLK240.00{0 20}p, G{dff_basic1/Q}

CLK380.00{0 40}p, G{dff_basic2/Q}

CLK4160.00{0 80}p, G{dff_basic3/Q}

CLK5320.00{0 160}p, G{dff_basic4/Q}

CLK6640.00{0 320}p, G{dff_basic5/Q}

CLK71280.00{0 640}p, G{dff_basic6/Q}

GeneratedMasterGeneratedMasterWaveform

ClockSourceSourceClockModification

-------------------------------------------------------------------------------

CLK2CLKdff_basic1/QCLKdiv(2)

CLK3dff_basic1/Qdff_basic2/QCLK2div(2)

CLK4dff_basic2/Qdff_basic3/QCLK3div(2)

CLK5dff_basic3/Qdff_basic4/QCLK4div(2)

CLK6dff_basic4/Qdff_basic5/QCLK5div(2)

CLK7dff_basic5/Qdff_basic6/QCLK6div(2)

由于我最终的目的是想把每一级的clk transition time给遗传到下一级,看看最后他的transition time是否过大,但我在看每一级的setup和hold的时候永远都是每一级都是一样的,是不是我的generated clock产生的有问题?

第三,我用set_clock_transition这个命令去给clk加transition time,但不论我加不加所有的setup 和 hold都不会变化,是不是有其他的设置我没有开?

由于是第一次用,对于这些电路的概念很多也是临时补起来,难免有疏漏。如果有低级的错误还请指正啊!

不知道是不是没有把问题说清楚

我最一开始只create了一个clk,然后发现由于前一级的输出是下一级CLK的输入,报出来的结果是CLK的口除了第一级都没有加上clk,而且再报路径的时候只到第一级就结束了,不会用后面几级的任何信息。

我就用create generated clock把剩下6级的CLK输入都相当于有一个generated clock。希望能看到每一级CLK的transition的信息,

生成的报告分了7个CLK,这个报告里intr这一项每一级都会叠加,但transition时间每一级都是一样的,是不是设置出了错呢?

transition time 肯定可以满足要求的