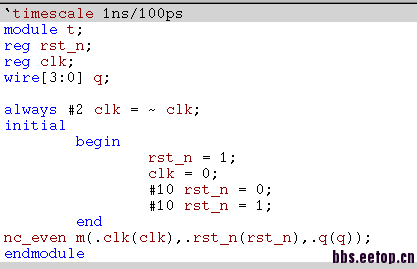

dc综合简单计数器

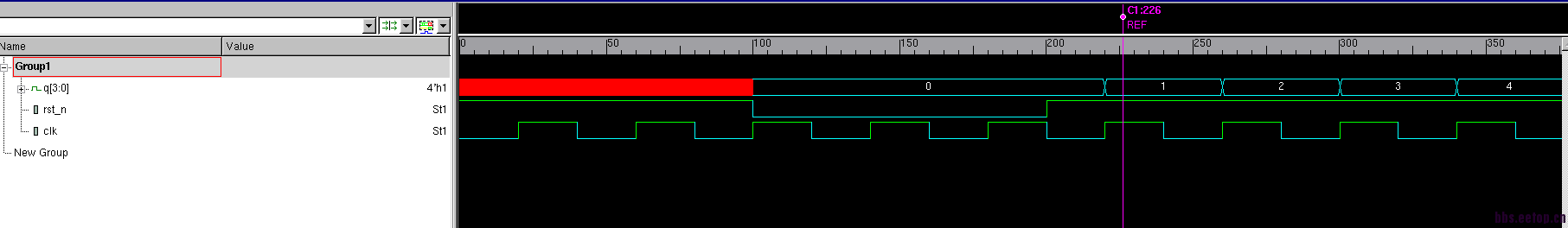

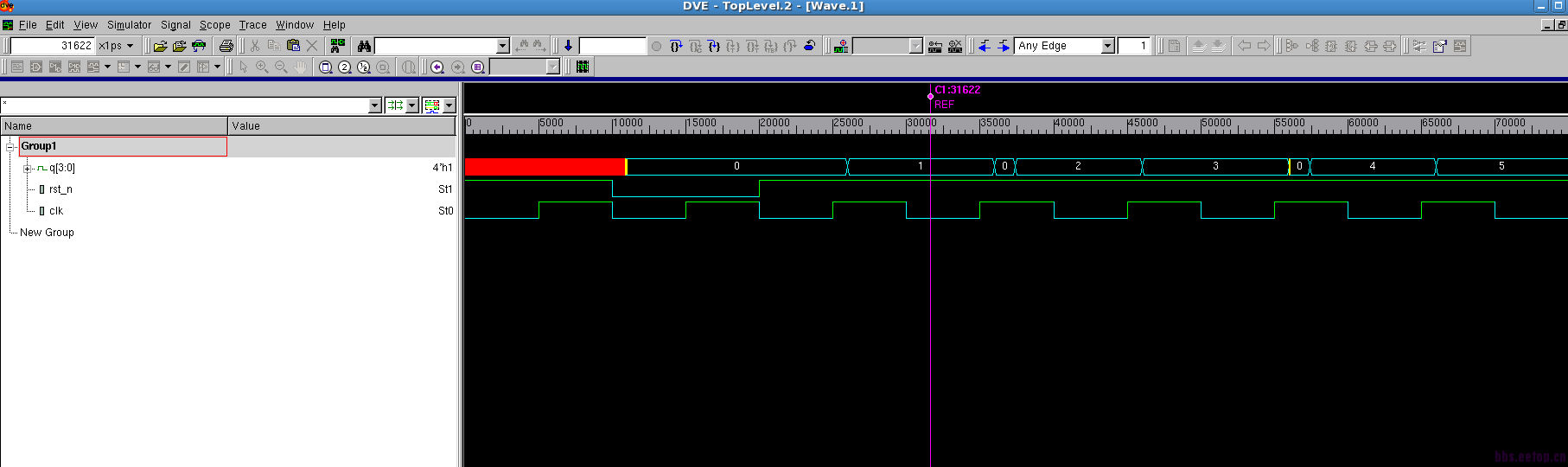

一、正确的波形当然是时钟每来一个上升沿计数加1了,VCS验证没有问题,但是经过DC后加入网表以及延时文件后再做VCS验证发现波形

就不对了,下面贴出这两个波形。

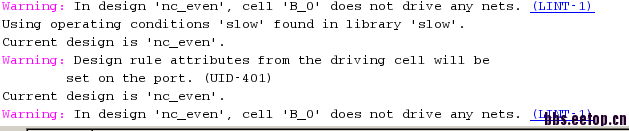

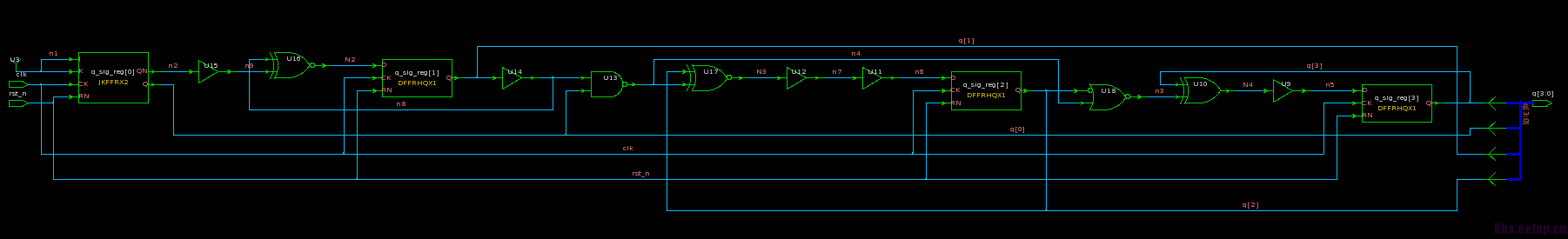

二、DC中出现了0个错误几个警告,警告内容的cell我没能找到,警告图和综合后的原理图也贴了上来。

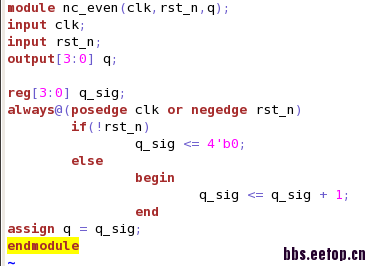

三、贴出了写的源文件、测试文件以及脚本。

四、没能找出到底是为什么,大家看看是哪里出问题了呢,谢谢!

下面是脚本

remove_design -all

set verilogout_show_unconnected_pins true

set active_design nc_even

set active_libnc_even_lib

define_name_rules MY_RULES -equal_ports_nets

analyze -format verilog ./verilog/nc_even_lib/nc_even.v

elaborate nc_even

current_design $active_design

uniquify

link

remove_unconnected_ports -blast_buses [get_cells -hier *]

check_design

set_operating_conditions -max slow

remove_wire_load_model

set all_in_ex_clk [remove_from_collection [all_inputs] [get_ports clk]]

create_clock -period 10 -waveform [list 0 5] [get_ports clk]

set_clock_uncertainty1.75[get_clocks clk]

set_dont_touch_network [list clk rst_n]

set_false_path -from rst_n -to [all_outputs]

current_design $active_design

set_input_delay -max 5 -clock clk $all_in_ex_clk

set_input_delay -min 0 -clock clk $all_in_ex_clk

set_output_delay -max 2 -clock clk [all_outputs]

set_fix_hold clk

set_max_area0

set_drive 0 [list clk rst_n]

set_driving_cell -library slow -lib_cell INVX1-pin Y $all_in_ex_clk

set_load 0.2 [all_outputs]

current_design $active_design

check_design

current_design $active_design

compile -map_effort medium

current_design $active_design

check_timing

change_name -hier -rules MY_RULES -verbose

set_fix_multiple_port_nets -feedthroughs -all -buffer_constants

current_design $active_design

write -format verilog -hierarchy -output ./mapped/$active_lib/$active_design.dc.v

write_sdf -version 2.1./mapped/$active_lib/$active_design.dc.sdf

write_sdc./mapped/$active_lib/$active_design.dc.sdc

write_script -hierar -out ./mapped/$active_lib/$active_design.dc.script

report_timing > ./reports/$active_lib/time_report_$active_design.rpt

report_area > ./reports/$active_lib/area_report_$active_design.rpt

report_lib csmc018_max >./reports/$active_lib/csmc018_max.lib.rpt

report_constraint -all_violators > ./reports/$active_lib/vio_report_$active_design.rpt

#report_timing

report_timing -delay max

# report_timing -delay min

report_constraint -all_violators

report_cell

网表的仿真波形是对的啊

不知道你说的不对是不是指仿真波形中,计数器1到2中间有其他值?这是正常的

对的,就是计数器之间有其他值存在,这是正常的?为什么啊。这样不会造成误差吗

计数器多个bit,每个bit就是一个寄存器,因为延时的差异,这4个寄存器的输出不是同时翻转的。要实现严格同时翻转有点困难,后端最多就是做是时钟树,调整这4个寄存器的时钟延迟到非常接近

没有你说的所谓误差,数字电路是基于时钟节拍的,计数器中间的过渡值不会被同一时钟采到,不用担心

如果是该计数器的结果做逻辑后同步到其他的时钟,一定要先在本时钟域先打一拍

嗯,原来是这样,谢谢!不过最后一句没有看懂,一定要现在本时钟域先打一拍。能细说下吗。谢谢!

因为异步时钟间的相位不固定,做同步电路时,这些计数器结果做逻辑后,其中间值可能导致毛刺出现,就可能被异步时钟采到,而这些中间值并不是希望存在的,所以不能在异步时钟域保存下来

简单点说,原则就是带毛刺的信号在同步前,先要消除毛刺。

相对于你的原帖,有点扯远了。另外,这些问题应该发在asic板块更合适

好的,意思就是说这个计数器逻辑如果用作后面电路的逻辑的话,首先要消除毛刺,可以采用在后面加一个寄存器采样的电路实现,是这样吗

感觉你对时钟和寄存器的理解还不是很到位。DFF只取时钟正跳时候的值,其他时间的都是dummy(前提是要保证在时钟正跳前后一段时间内data是正确的,这里涉及到setup time和hold time)。你可以想象一下最简单的加法器,进位的时候总是会有延时的,但是只要延时不出现在正跳的时候就没什么影响

原来你的是正确的啊,,哈哈,,

顶贴赚积分