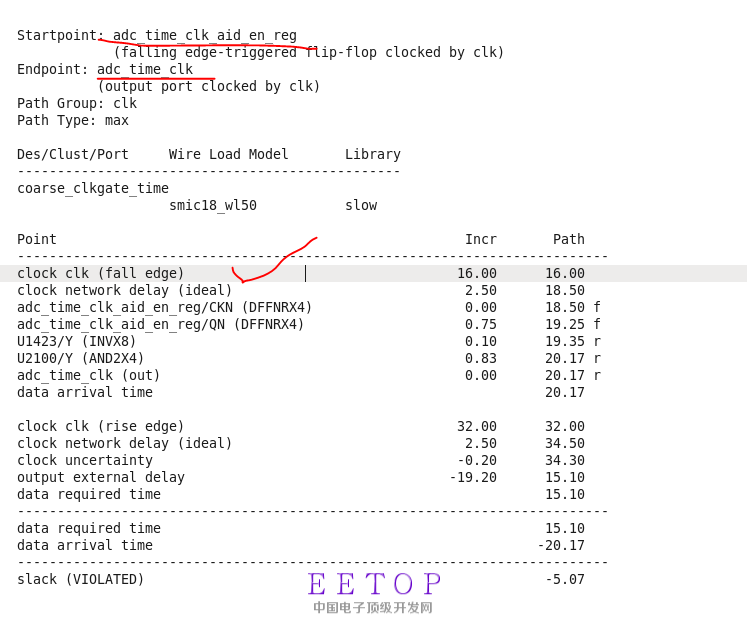

DC中怎么设置下降沿触发 输入延迟问题

adc_time_clk_aid_en 是时钟下降沿触发输出的信号,因此它的输入延迟是从clock 的下降沿开始计算的。这样 该信号的输入延迟就多算了半个周期,结果就违例了。请问各位该怎么设置该信号的 输入延迟呢。该信号是内部信号,不是端口。急,急,急,多谢各位!

adc_time_clk_aid_en 是时钟下降沿触发输出的信号,因此它的输入延迟是从clock 的下降沿开始计算的。这样 该信号的输入延迟就多算了半个周期,结果就违例了。请问各位该怎么设置该信号的 输入延迟呢。该信号是内部信号,不是端口。急,急,急,多谢各位!

adc_time_clk是输出给其他模块用的信号吗,在接收端的模块这个信号是被clock的上沿抓还是下沿抓?它的output delay设置为19.2是否太大了?

如果你这个结果只是自己模块综合的话,放在整chip里面时不一定有violation了,就看19.2的output delay是否够用。

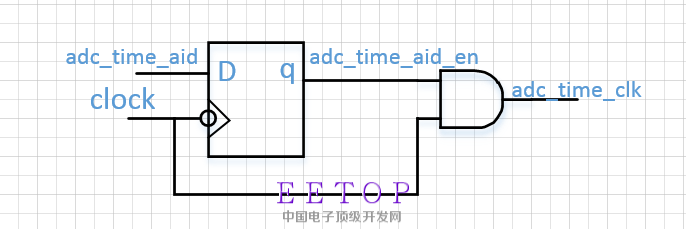

又仔细看了一下,你的adc_time_clk实际上是一个门控时钟,是clock用下降沿抓了门控使能信号后,再与上clock得到的。adc_time_clk其实就是和clock有相同属性的时钟信号,你对它又在clock域下约束output delay是不合理的

谢谢回复,是这个样子的,那么对adc_time_clk不做输出延迟约束么? 具体怎设置,求教。

这个需要根据你的具体设计需求来,如果生成的adc_time_clk与前面的clock不再有关系,可以重新定义它为一个时钟,如果它跟前面clock属性一样,你都不需要对它做约束了,放在整chip里面时它就是内部时钟信号而已。

adc_time_clk是数字的输出端口,去驱动ADC。我第一次做综合,请指教。

带上ADC的hard block一起综合啊,ADC的lib里面提供adc_time_clk以及数据信号的时序信息。一起综合时就属于内部信号,自然就会检查时序了。这个就类似于SRAM控制器,你调用的sram在综合时是以lib提供的,它里面涵盖了sram的clk以及data的时序信息。你一定要说单独综合SRAM控制器而刨去内面的sram这个hardblock,那你觉得给sram的clock以及data等接口信号该怎么约束?跟你这个ADC接口信号道理是一样的

时序模块是单独一个模块,ADC是我自己做模拟电路。adc_time_clk是我时序模块的一个端口。