关于cts前后generated clock的source latency的问题

时间:10-02

整理:3721RD

点击:

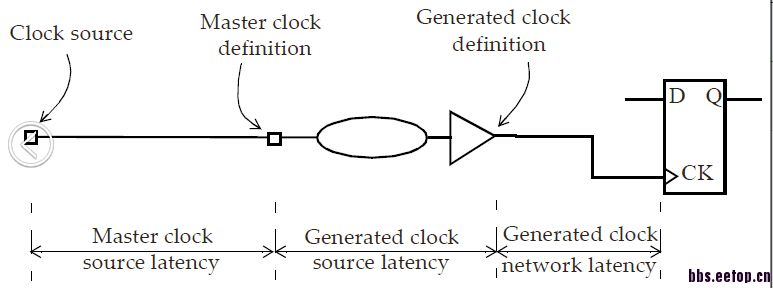

genreated clock 的 source latency是从master clock defination point 到 generated clock defination point,

那么请教大家: 当cts之后 generated clock的source latency是不是就不是之前通过 set_clock_latency -source 设置的值了,就变成

master clock的 insertion delay了(实际的延迟了)

首先,我觉得generated clock到source latency应该不用设置吧,如果非要设置到话,CTS之前应该跟它到master clock到source latency一样,因为CTS之前clock到network latency都是零.

其次,CTS之后,我觉得应该也不用设置,因为如果在计算generated clock 上的timing path的delay时,工具会从master clock的的latency开始计算,就你的图中的例子来说,如果计算到最后一个FF到delay应该是mater source latency+generated clock source latency+generated clock network latency.

如果你CTS之后自己给generated clock设置了一个source latency(假设大小为1.5ns)的话,那么到最后一个FF的latency 就变成了 1.5ns + generated clock network latency,这实际上是不对的.

以上是本人理解

多谢!