power signoff

时间:10-02

整理:3721RD

点击:

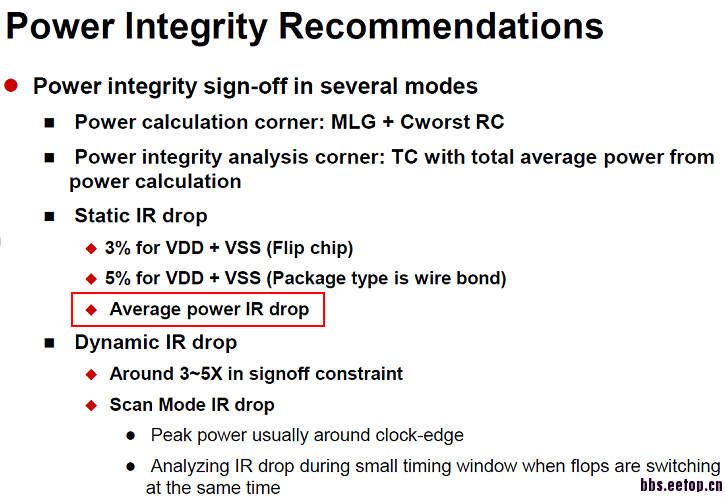

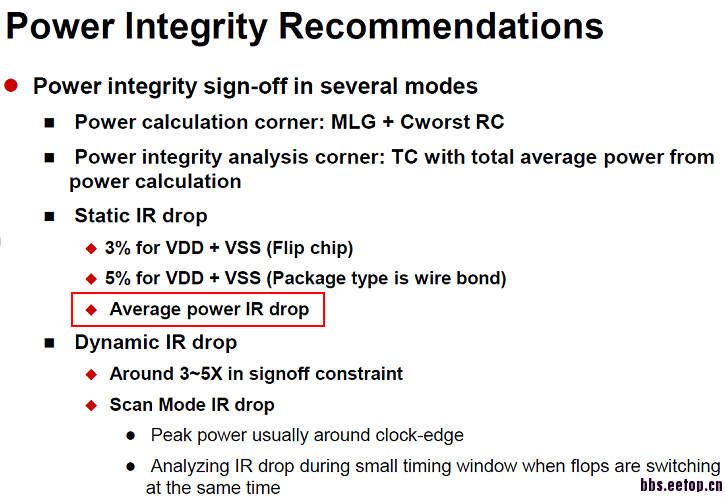

如下图,这是foundry给的power signoff的建议。有几个点不太懂。power calculation 和power integrity analysis为什么不使用一个corner呢?我通常说的IR drop分析应该是指的power integrity analysis吧,所以static和dynamic IR drop 是以TC corner为准吗?谢谢!

顶一下!还有就是红框里面的那句话不太懂,求大神现身!

通常是tc或者wc corner的, guideline通常很严格,具体可以根据经验等来

你做多了对这些标准也就淡化了,就那么回事

谢小编回复。根据目前IR Drop的结果来看,WC和TC的情况还好,静态VDD + VSS大概在2%以下。但ML很差,超过了5%。所以看了foundry给的建议后就有点疑惑了。我们通常都是以最差的情况来约束设计的,但建议里面却是以TC为标准的,有点奇怪!那么根据小编的经验,我上面的IR Drop结果可不可以接收呢?

应该行, power 分析结果和分析过程和方法强相关,可以说不同的方法可以导致不同的结果

简单的 就肉眼看看好了, 没太多兴趣深究

是的,我用PrimeRail跑同一个design每次跑出的结果都有些不同。不过量级还是不变的。