generate clock balance 问题

时间:10-02

整理:3721RD

点击:

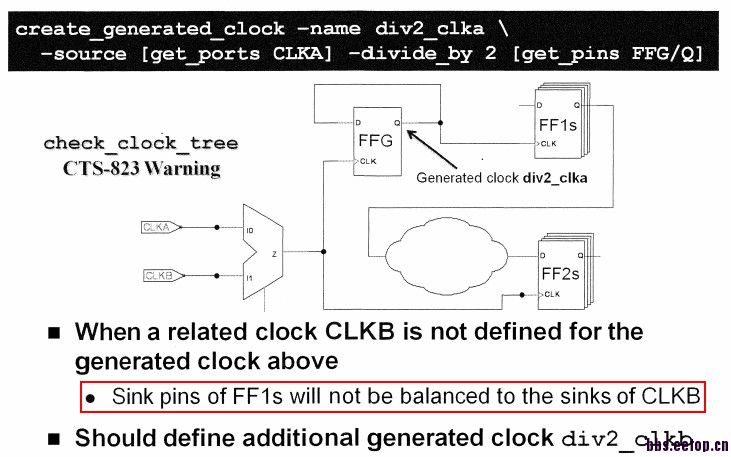

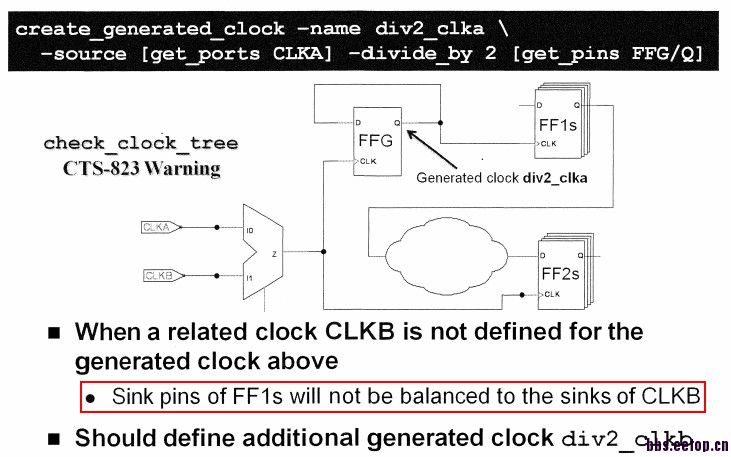

在看CTS student guide 时发现如下问题,请问红框内的话该怎么解释呢?

你不在FFG的后面定义generated clk 时钟是不会穿过FFG的后面的时钟也也不会做balance了,还有你的在FFG的后面最好加一级buffer在buffer的后面去定义generated clk......要不然就把FFG上的时钟挤掉了.......

看错了 ....... 你这个是两个时钟选择后的 我们这边的处理就用最快的时钟去约束...不好意思一上来就理解错了.......

对,其实写一个就行了,

那UG上面说的这句命令create_generated_clock -name div2_clkb -add \

-source [get_ports CLKB] -divide_by 2 [get_pins FFG/Q]

应该是不需要了吧? 谢谢回复!

那UG上面说的这句命令create_generated_clock -name div2_clkb -add \

-source [get_ports CLKB] -divide_by 2 [get_pins FFG/Q]

应该是不需要了吧? 谢谢回复!

也可以有,怎么说呢, 都有,和没有都行, clkb