encounter调用模块~(十万火急,救命救命!)

我想用encounter分别对diff和veri模块进行布局布线,然后veritop模块再以类似stardardcell形式调用。

问题来了:

我对diff和veriAC_AB模块布局布线后生成diff.lib, diff.def, veriAC_AB.lib,veriAC_AB.def 。

用abstract进行抽象,可是abstract说我没有电源和地两个端口。(不过还是抽象出diff.lef和veriAC_AB.lef了)第一个问题:怎么加电源和地端口。

最后用encounter对veritop调用diff.lef和veri.lef后,没有像一些书上写的那样。书上如图:书上例子是将右边的三个模块(就像我的diff和veriAC_AB模块)手动移动到core area内部,并且power ring和power stripe会绕过模块,并且对模块内部的电源线进行布线。

(书上例子)

(书上例子)#####################################################################问题又来了:

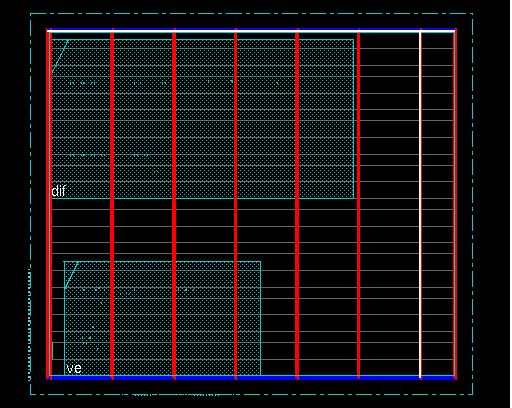

而我的设计,diff和veri模块是如下图输入的。显示也如下图,根本没有模块。后来模块是在place standardcell时候出现的(如图),和书上的差距太大了。尤其是电源线,根本就没有(如图)。

第二个问题,怎么配置如书上那样调用模块。介绍几本书最好!谢谢

1 第一个应该是在抽lef时,在电地上打上label吧

2 书里的子模块应该是设成 partition或当成macro,而你的做法是把两个模块当成了std cell了。std cell在floorplan 视图里是看不到的

有什么不对的地方请楼下的补充更正了~

都是abstract提取lef的问题

1,在版图中电源地上打好label,这样abstract才能提出端口,同一个端口,比如电源,没有连接到一起的话,每个电源都要打label.

2,你这2个模块提取的类型不对,你现在用的是core类型,这样是作为标准单元使用,在encounter中,布局是不可见的,要提取成block类型,才能像练习的样子.

abstract怎么用呀!我抽象的时候总是没法creat round pin ,抽象成block更是产生空的lef文件(但是抽象成core却能生成lef文件),谁有这方面的经验 介绍一些行吗,介绍几本书,文档也行呀! 或者有没有其他什么软件能够生成lef使用方便点的! 万分感谢

destiny21 这位大侠说的对啊,

我想补充点,电源地在abstract时应该特别处理,例如是ring还是strap。

学习了,留个记号

雁过留声!

如果是 partition block 来做toplevel integration ,不是用abstract 出lef,

edi本身能对partition本身做lef,

lefOut即可,

这样顶层的conf 里面可以把 partition block的lef 写在 rda_Input(ui_leffile) 里面可供调用,

顶层做power的时候要先用globalNetConnect ,否则连不上的

模块最好mark成Block,否则std cell当然看不见了, 看leffile,

你的.lib是怎么生成的? do_extract_model 么

如果是 partition block 来做toplevel integration ,不是用abstract 出lef,

edi本身能对partition本身做lef,

lefOut即可,

这样顶层的conf 里面可以把 partition block的lef 写在 rda_Input(ui_leffile) 里面可供调用,

顶层做power的时候要先用globalNetConnect ,否则连不上的

模块最好mark成Block,否则std cell当然看不见了, 看leffile,

你的.lib是怎么生成的? do_extract_model 么

partition来处理吧

学习一下!

学习一下……

请问你的.lib怎么生成的啊?