Calibre PEX抽取多层次数字模块寄生的问题

时间:10-02

整理:3721RD

点击:

使用CALIBRE PEX来抽取多层次的数字模块的寄生参数,使用的GATE-LEVEL,目标是抽取出整个模块的SPEF文件再放到PT中做STA。可是发现PT不认,报SPEF中很多节点没有找到。但是同样的RUNSET,跑小的单层次的模块就没有问题,请问各位大大有没有碰到过这种情况呢?是我哪里没有设置好吗?

PEX 不能抽门级吧,都是晶体管级别的,因为是从layout里面抽取,

门级抽取RC要用StarXT或者qrc ,calibre不能抽门级

啊,这样,谢谢ICFB大,明天我去试试~

那请问在calibre pex界面中output-》 Extraction type--》 如果选gate level是什么意思?

试验了一下,选gate level应该就是忽略transistor参数的提取了,只是需要给一个hcell file,没有这个提出来的仍然是transistor-level的

对, starxt抽取的是gate到gate的掩饰, 不看晶体管的,

gate本身的延时,他把 gate 看成skip cell的,就是不进去再进行抽取,因为里面就是晶体管了,

pex 怎么抽取都是晶体管级别的,

谢谢

Calibre 是可以抽取门级的寄生参数的哦。

学习中!谢谢!

用于抽取数字的规则文件和模拟的文件是一样的吗?

你好,关于这个问题我也非常疑惑,你说calibre可以抽门级,可是2楼说pex不能抽取门级的,我想问如果calibre可以抽取门级的,具体要怎么设置,为什么我这边产生的spef文件放到PT中会显示很多net不识别,和小编的问题一样,跪求大神给予帮助

网上应该有配置脚本吧

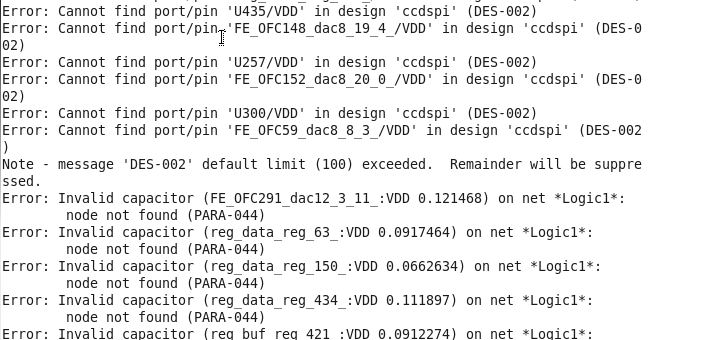

昨天又重新修改了下calibre 做pex的设置,现在生成的spef文件到pt跑了下,问题少了很多,用report_annotated_parasitics反标了下,之前的反标结果是一个都没反标上,现在的结果显示只有一条pin to pin 的net没有反标,相比之前好多了,以下是pt中的报错,奇怪的是这个spef文件中怎么会有VDD