astro时序分析结果和DC不同,且相差很大,为什么?

时间:10-02

整理:3721RD

点击:

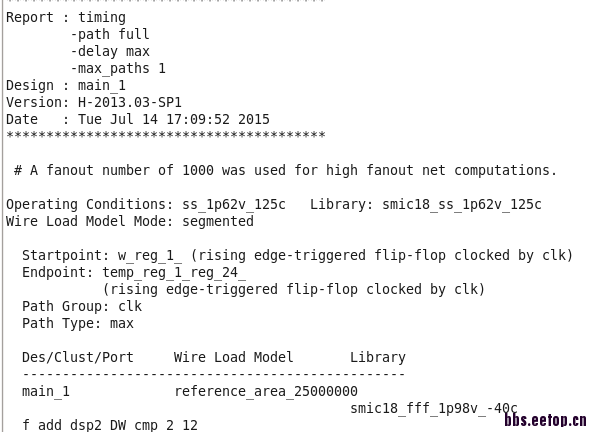

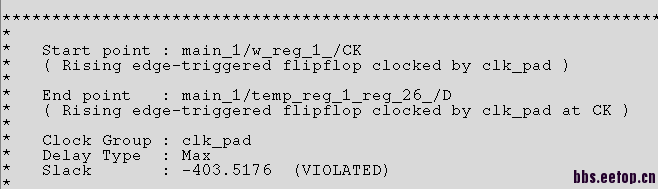

我用的smic-0.18um最新工艺,在DC中做的逻辑综合,综合后显示slack是正值,在170左右,导出.sdc文件和网表文件到Astro中做布局布线。如下图所示为DC中报告的最长路径,和它的slack报告:

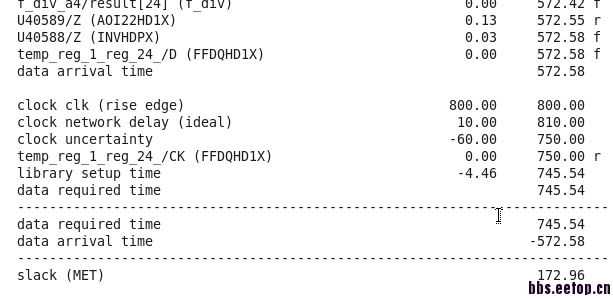

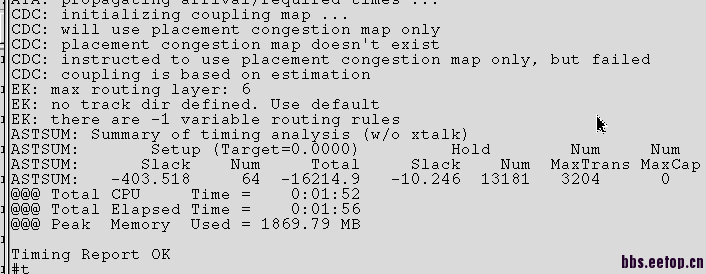

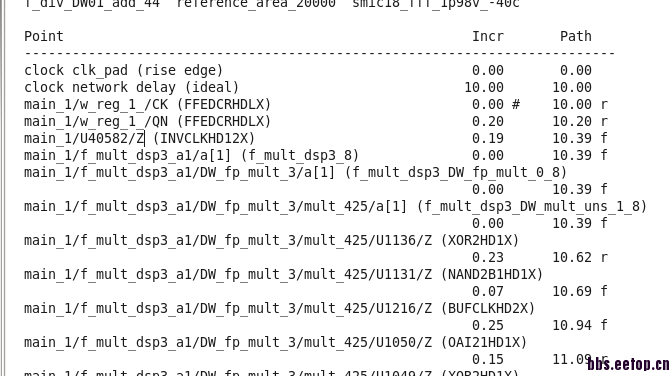

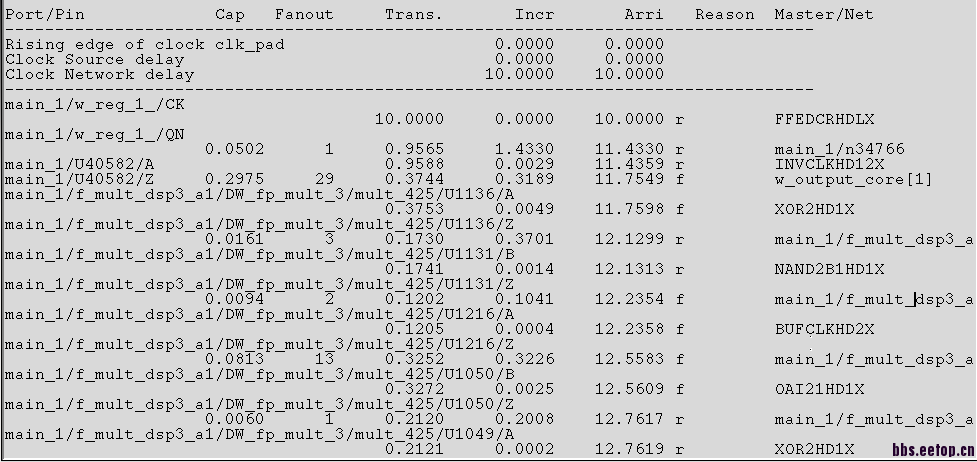

下面是导入到Astro中,在布局规划之前进行时序分析后得出的的时序报告信息,可以看到slack变成-400多了,整整减少了500多,而我的时钟周期才800。

DC中和Astro中分析的环境是相同的,都是fff和ss,但是slack相差甚远......

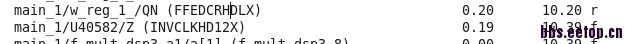

下面是Astro中最长路径的起止点,可以看到和DC报告中也是不同的:

不知道各位做后端的大牛们有没有遇到过相似的问题,还请各位大牛帮我找找问题,出出主意,谢谢各位了,感激不尽^_^

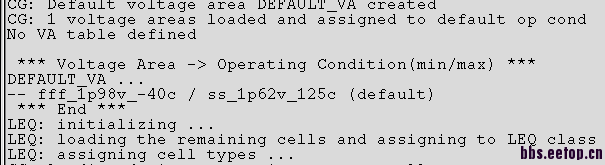

补充说明一下,Astro中进行时序分析用的是LM库,LM库中的ss/fff等db文件是从前端的db文件生成的,里面的信息应该差不多的。

Astro和DC用的是几乎相同的信息,但是时序分析得出的结果相差怎么会如此之远?

且,我又用smic-40nm工艺做了一下,DC中时序分析结果slack=+461,可是导入Astro后,变成了slack=-229(用的也是LM库)。这完全不能让人接受...

望各位大牛指导迷津

忘了, 10年前的astro

report_timing path in detail, compare the gate delay seriatim

Thank you for your reply. I have already done that, but I found that the delay informations generated by DC are not same as that generated by Astro:

The path is not identical, and even the delay informations of each cell are not coincident. For example:

报同一条path,比较每个cell和net的delay,transition和cap

place之前,按理不会差太多

请问一下,您有没有在ICC或者Encounter里面遇到过这种情况,就是DC报告的路径和导入ICC/Encounter后报告的路径相差很大?

dc 里是没有物理位置的所以没有net delay

astro是place之后有物理信息的, delay当然变大了

可是,我用smic-40nm工艺进行综合后的最长路径的data arrival time=277.68,导入Astro后时序分析结果显示最长路径的data arrival time=977.7,而总的时钟周期才800,如果是位置信息引起的net delay的话,那也不可能差这么多吧?且这个综合后的网表是我采用过时序优化后的结果,按照Astro的报告信息,最长路径延时都比时钟周期好长,这不是说这个设计根本就无法实现嘛,之前在用0.18um工艺做,看来这更不可能了吧?