power plan后的congestion问题

最近在学习ICC,遇到一点问题,希望能得到大大的指导。布局、VFP再跑一次之后congestion的分析,感觉congestion很少

图1:

在做了power之后,又分析了一下congestion,感觉增加了挺多

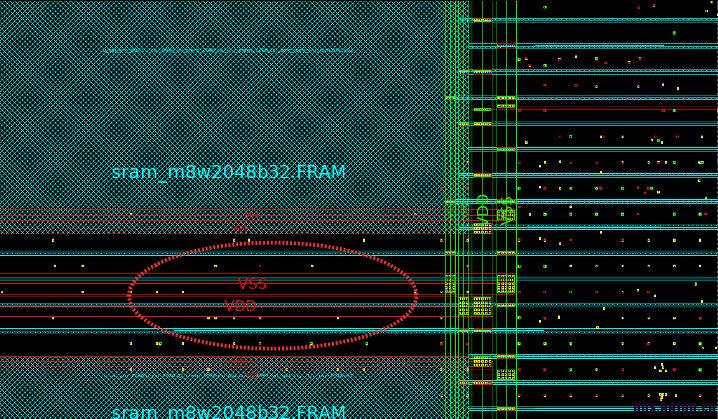

图2:

放大细节发现,standard cell的rail连到了macros(sram)之间的位置(set_keepout_margin=10,hard type),估计这是congestion增加的原因,虽然知道可以拉开距离,但是像这种具体的情况不知道该怎么解决,实在有些迷茫,希望能得到大侠的帮助,非常感谢!

图3:

power打的太多了吧,建议route完看short的地方 就明白了

感谢版大的回答!我正在绕线等着看结果,不过感觉要很久。看来这个power做的不好,我原本以为只是standard cell的pg rail的问题,不知道还会有什么其他可能的问题,估计等到看结果会有更直观的认识。

什么工艺?就4层 布线资源,太少了吧, 怪不得打完power就不行了,

刚欢送完同事回来就看到了版大的回复,非常受宠若惊。我们采用的是global foundry 0.18um工艺,因为之前流片的相同工艺的模拟芯片只用到了4层金属,而且这颗芯片的数字规模也很小(45%左右的是sram模块,80%的芯片利用率),所以想当然的希望这颗芯片能通过4层金属实现了。

metal4 是9K厚度么,利用率这么高,不好做的, 打power要有些讲究,

memory本身就占用4层金属,相当memory本身都无法提供太多route resources,

我看了一下绕线的layout,发现那些部分走线比紧张(版大提到的金属层少走线资源少应该是造成这个问题的主要原因),想到的办法是:1.首先将相应的sram array间距拉大一些,2.因为sram已经自带了一圈power ring(2um),额外加的那一圈的power ring考虑不加了(不知道pns会不会有问题,sram相对较多),3.将某些sram调整位置和方向,并align pin以减少折线,减少额外占用的绕线资源。目前想到的就是这些,先run试试看。

呵呵,版大一看就知道是9KA的,M4确实是的。那一般这种情况下,利用率多高会比较合理呢?我还不是特别清楚。

对,memory有ring 就不用另外加ring了,只要straps tap上就行了,

m4 的设计,利用率很难到80%以上, 70% 左右差不多了,

嗯,感谢版大的解惑,我再试试看!