DC中 compile -scan没有把DFF转换成SDFF

全部没替换还是部分没替换?

如果部分没替换,是正常的。

全部没有替换啊!

帅哥,是全部啊,我都纳闷了····!

是否设置dont use这些cell了

我发现了一个问题datasheet整体芯片介 绍是说明有scan 的DFF的,但是我详细看verilog 和datasheet 每一个cell又没有关于这个类似的描述,spi 里面也没有关于scan DFF的描述,这个是不是有特别做DFT的库呢?难道和DC的库不一样?

我肯定是你把SCAN FF设成dont use了

如何修改回来··请指导!

找到你设置这句話的地方把这句话mask掉就行了啊

我就设置了一下输入输出,然后直接complier -sacn根本没设置SCAN FF设成dont use,这个有可能默认是这样设置,请问在那里修改?

可以提供更多的信息吗?谢谢兄弟啊!

你做DFT吃得是netlist还是ddc文件,我吃netlist跑DFT整个模块就发现8个DFF,换ddc就可以跑了,不晓得为啥

1,查看log,是否有error,或者严重的warning,compile命令是否顺利执行

2,查看dont use设置

这个是compiler -can 的警告!Warning: No scan equivalent exists for cell delay_pipeline_reg[0][13] (DFCNQD1BW P7T). (TEST-120)

Information: There are 138 other cells with the same violation. (TEST-171)

如何查看don't use 设置命令是report什么?具体看那个···谢谢你的解答!

我吃的verilog ,DFF多少和你设计有关吧!难道你的太深奥··我理解不了,可以详细解释一下吗?兄弟!

自己看一下库文件,是否有scan cell。从你的warning来看,要么库中没有scan cell,要么库设置不对

应该是没有的!

我现在找到了有scan cell的库,那么我compiler -sacn DFF全部转换成SDFF····由于我读入的verilog文件,根本就没有SI这些端口,我是不是要修改我的设计···把SI(扫描链的input)加进去?

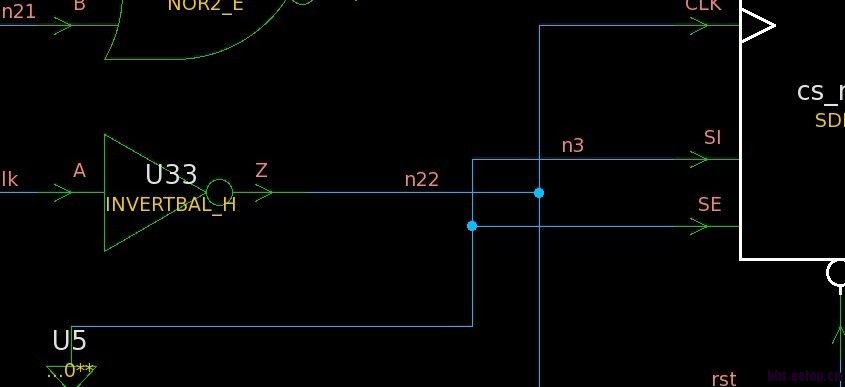

你看现在出现了这种情况SI直接接地了!看图

si是dft 扫面链的端口,让dft的人连接,综合的人不用管

嗯,谢谢啊。兄弟你会dft吗?我有一个问题哈,因为我设计里面有状态机,里面状态更新是时钟的下降沿触发,而其他电路寄存器就是时钟上升沿触发,那么compiler -scan 就会产生两种寄存器,那么扫描链数据输入就是有两个 si1和si2 ,那么这两种类型寄存器需要连接在一起吗?还是让它由两个扫描链分开链接这两种寄存器?

两种寄存器都是由一个时钟源clk来给信号的,那么下降沿触发寄存器前面会有一个反相器,那么我dft_drc的时候产生这种DRC错误,那么我应该如何fix呢?

错误信息:clk ( Warning: Clock clk can capture new data on TE input CLK of DFF uut3/cs_reg[1]. (C6-1)Source of violation: input CLK of DFF uut3/bit_cnt_reg[3].

)

这种warning我们是不管的,但是dft具体如何做,我就不太清楚了

看你的警告应该是你的库有问题,以前我也遇到过。你看你的扫描单元(SDFF)在lib中是否有"扫描测试"的属性,尤其是“TD/SI/SE”端口。另外如果你有别的工艺库你可以试一下别的工艺库能够替换,另外再将多个厂家的工艺库进行对比——只要对比扫描单元你就可以知道了。

si是dft 扫面链的端口,让dft的人连接,综合的人不用管