DC综合后.net网表文件的显示格式问题

如果我想让我综合之后的.net文件中显示格式如下:

HDR_DRNQ_1 q_reg_1 ( .D(din[0] ), .CK(clk), .RDN(rst_n), .Q(q[1] ) );

HDR_DRNQ_1 q_reg_0 ( .D(din[1] ), .CK(clk), .RDN(rst_n), .Q(q[0] ) );

而不是

HDR_DRNQ_1 q_reg_1_ ( .D(\din[0] ), .CK(clk), .RDN(rst_n), .Q(\q[1] ) );

HDR_DRNQ_1 q_reg_0_ ( .D(\din[1] ), .CK(clk), .RDN(rst_n), .Q(\q[0] ) );

请问 define_names 和 change_names该怎么写呢?

change_names -rules verilog -hier 即可

小编大人,您终于来了,可是我写着那句话的啊,是不是因为我还写了其他的,您帮我看看,这是我的 Link_lib.path文件中的:

define_name_rules rule0 -restricted "\!\@\#\$\%\^\&\*\(\)\/\-\"\{\}" -case_insensitive -map {{{"%s_%d","%s[%d]"}}} -type net -target_bus_naming_style {%s[%d]}

define_name_rules rule1 -restricted "\!\@\#\$\%\^\&\*\(\)\/\-\"\{\}" -case_insensitive -map {{{"%s_%d","%s[%d]"}}} -type cell -target_bus_naming_style {%s[%d]}

define_name_rules rule2 -restricted "\!\@\#\$\%\^\&\*\(\)\/\-\"\{\}" -case_insensitive -map {{{"%s_%d","%s[%d]"}}} -type port -target_bus_naming_style {%s[%d]}

define_name_rules rule3 -remove_port_bus

define_name_rules rule4 -case_insensitive -map {{{"_reg_%d","_reg[%d]"}}}

这是我的run.dc.tcl文件中的:

set bus_dimension_separator_style "[]"

#set bus_naming_style{%s_%d}

set bus_naming_style {%s[%d]}

change_names -rules verilog -hier

change_names -rule rule0 -hierarchy

change_names -rule rule1 -hierarchy

change_names -rule rule2 -hierarchy

change_names -rule rule3 -hierarchy

change_names -rule rule4 -hierarchy

write -format verilog -hierarchy -output ./report/$module.net

结果就变成了:

module test ( clk, \din[1] , \din[0] , rst_n, \q[1] , \q[0]);

input clk, \din[1] , \din[0] , rst_n;

output \q[1] , \q[0] ;

HDR_DRNQ_1 q_reg_1_ ( .D(\din[0] ), .CK(clk), .RDN(rst_n), .Q(\q[1] ) );

HDR_DRNQ_1 q_reg_0_ ( .D(\din[1] ), .CK(clk), .RDN(rst_n), .Q(\q[0] ) );

endmodule

太复杂了,就用verilog rule吧,没必要搞那么多,

恩 好的,我还纠结呢 这是毕业师兄写的,原本还想搞懂里面每句话到底有什么作用呢,弄了整整一个晚上 乱七八糟的感觉

小编大人,在最后问一个问题啊,我按您说的,只剩下最后那一个change_names -rules verilog -hier综合出来是这个:

HDR_DRNQ_1 q_reg_1_ ( .D(din[0]), .CK(clk), .RDN(rst_n), .Q(q[1]) );

HDR_DRNQ_1 q_reg_0_ ( .D(din[1]), .CK(clk), .RDN(rst_n), .Q(q[0]) );

我一直想把 q_reg_1_改成 q_reg_1 可以实现吗

很麻烦, 不如set_name改,

师兄写的问师兄啊, 学校里都这样, 流水的盘啊,

set_name是ICC的,Encounter我man了一下,没有这个命令啊。

说错了 是DC里面没有 set_name这个命令啊

干嘛要改成那样了,有啥目的么?

还真没有,就是想熟悉一下语法,运用自如吧 以后就可以按照自己想要的输出格式来写啦

你真是闲的有空, 上班了估计你没这个时间,

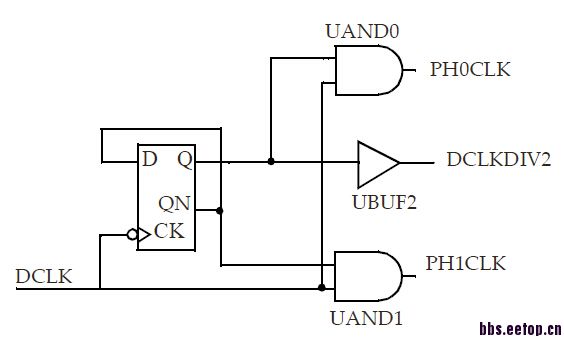

小编大哥,再问一下,这是一个电路小模块,底下定义时钟的语句有:

create_clock 2 [get_ports DCLK]

create_generated_clock -name DCLKdiv2 -edges {2 4 6} -source DCLK [get_pins UBUF2/Z]

我想问下,刚开始写sdc文件的时候,我并不知道会有一个例化名是 UBUF2的单元啊,那我该怎么写呢?

综合前 写在 hier 边界上,综合后可以再改的

恩 我之前看到过您在另一个帖子中说过,可是还不是很理解啊,还望不吝赐教,感激不尽。这个hier 边界怎么回事呢,我理解的hier边界就是不同的module之间的连接。那如果我上面图中的器件单元都在以个 module中,岂不是就没有hier 边界了吗?

理解了,综合之后因为知道了例化名,可以再生成的sdc文件中手动修改,然后再重新DC