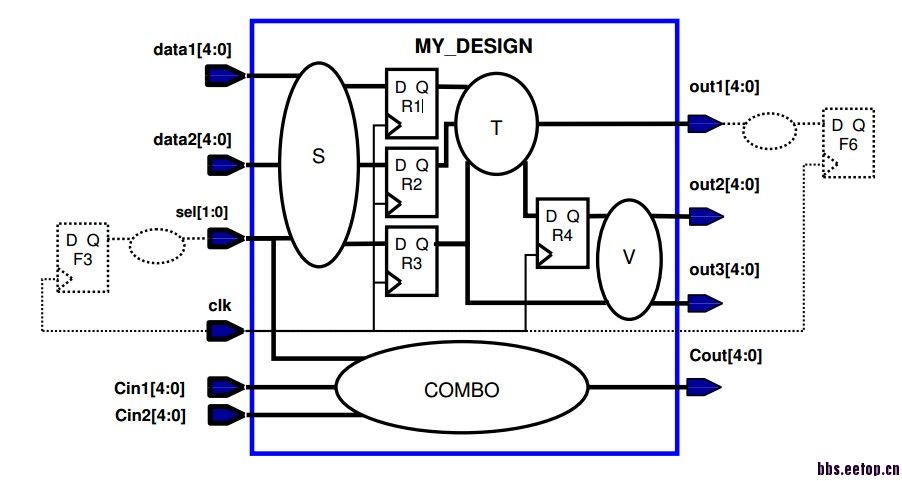

clock_uncertainty和set_input/output_delay的计算问题

时间:10-02

整理:3721RD

点击:

请教一下大家:

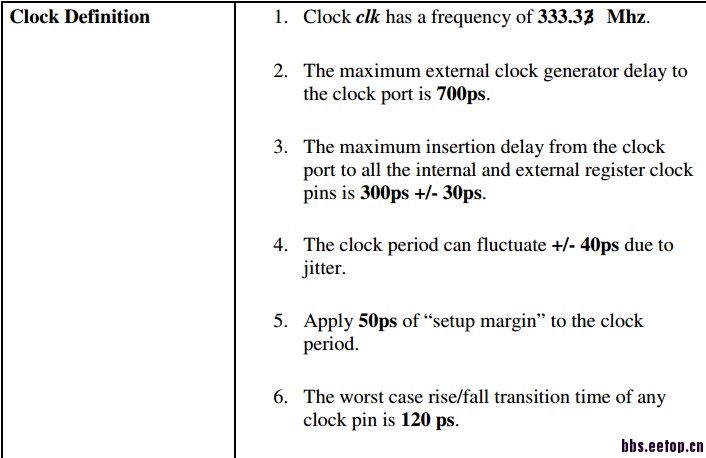

1、clock_uncertainty不是指时钟的抖动吗?不太理解下面的定义方法,另外,为什么时钟有什么setup margin?建立时间不是在寄存器的D端?

# The +/-30ps internal clock delay variation to register clock pins results in a 60ps worst case skew or uncertainty, if you launch

# late (+30ps) and capture early (-30ps)r; Add 40ps due to jitter and 50ps for setup margin;

# This equals 150ps or 0.15 ns of total uncertainty.

#

set_clock_uncertainty -setup 0.15 [get_clocks clk]

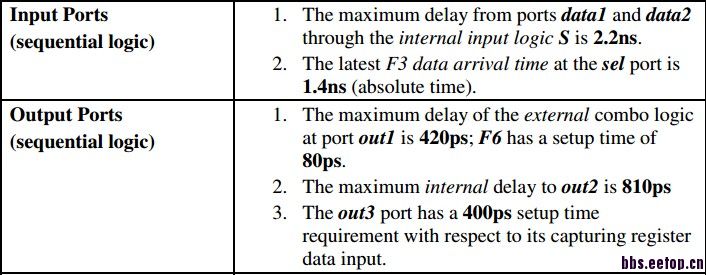

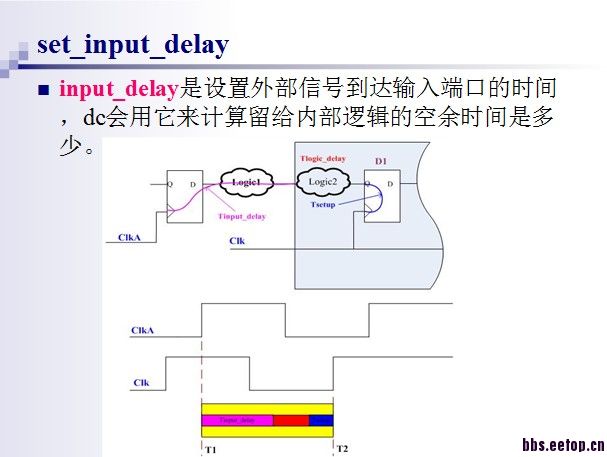

2、为什么input考虑到了时钟的延迟,而output不用考虑到,而且输出端口也是有建立时间要求?

# The latest arrival time at port sel is 1.4ns (absolute time). The total clock insertion delay or latency to the external

# registers is 700ps + 300ps or 1.0ns. Therefore, the relative input delay on the port is 1.4 -1.0 = 0.4ns

#

set_input_delay -max0.4 -clock clk [get_ports sel]

# The setup time requirement on port out3 is 400ps or 0.4ns with respect to the capturing register's clock.

# This is, by definition, the "set_output_delay" value

#

set_output_delay -max0.4 -clock clk [get_ports out3]

好问题 顶一下 同问

uncertainty include jitter and skew!

I think 50ps is skew value, andskew can affect setup time ,so called setup margin!

恩恩,好的,谢谢!

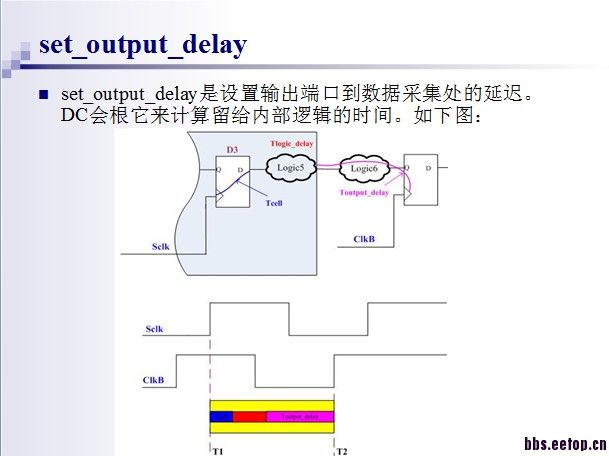

我看了下下面资料,输入输出延迟可不可以这样理解set_input_delay 算的是时钟端口到数据端口的延迟,所以考虑了时钟的延迟,而set_out_put算的是输出端口到数据采集处的延迟,可以不考虑到时钟?

1setup margin考虑的一般是后端实现时会在数据路径引入的network delay

2显然不是那么回事,你们坐等小编好了

我的理解是,把下游也考虑进来,输出寄存器到下游输入寄存器的路径是同步路径,set output delay指定的是下游要占用的时间

恩恩,好的,谢谢!