数字电路做DRC检查的时候出现的poly coverage的问题

时间:10-02

整理:3721RD

点击:

就是在做DRC检查的时候,出现poly coverage小于0.14的问题,其中有的是因为某个调用的单元本身单独拉出来做DRC就存在这个违例,有的是因为几个单元组合在一起的时候会报这个违例。我想知道这个poly coverage的检查机制到底是怎样的,为什么本来单独不存在这个问题的几个单元组合在一起形成一个新的组合逻辑的时候就会报这个错误

可能是組合做的時候有些圖形會重疊在一起只能算一塊面積的關係吧

单独一个block存在覆盖率不够的情况不需要理会的吧,到了整个chip拼装的时候还是报这个问题的话就填充电容,个人看法

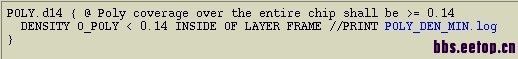

rule里面有这个error是如何计算的

直接按面积比计算

block的可以不管

只要最终coverage够了就行,不够就手动画一些没用的就行,也可以按3#说的做

顶顶顶