请教一个multicycle constraint的问题

时间:10-02

整理:3721RD

点击:

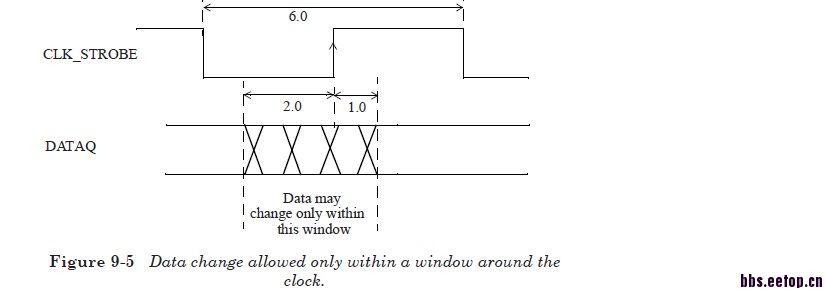

在“Static Timing Analysis for Nanometer Designs__A Practical Approach”一书的9.1.3小节中提到对于图中的timing要求下constraint的方法是:

set_multicycle_path 0 -setup -to [get_ports DATAQ]

set_multicycle_path -1 -hold -to [get_ports DATAQ]

set_output_delay -max -1.0 -clock CLK_STROBE \

[get_ports DATAQ]

set_output_delay -min +2.0 -clock CLK_STROBE \

[get_ports DATAQ]

我对这段constraint的理解如下,可是其中关于output_delay的max/min值的解释觉得有点不够清晰,大家可否帮忙解答一下呢?

1,不下set_multicycle_path的情况下,setup relation是从T1到T2,即T_internal + T_external + T_setup <= T_cycle

但是如果set_multicycle_path 0 -setup -to [get_ports DATAQ],则意味着setup relation变成了从T1到T1,即上式中<= T_cycle要变成0.

由于tool无法知道外部DFF的T_setup,只能假设为0,所以setup relation要求就变成了T_internal + T_external + 0 <= 0,

为了确保DATAQ只会在clk上升沿后1ns内变化(可看成是T_internal<=1ns),

通过要求 T_external最大为-1ns来告知tool T_internal最大为1ns:

set_output_delay -max -1.0 -clock CLK_STROBE [get_ports DATAQ]

2, 不下set_multicycle_path的情况下,hold relation是从T1到T1,即T_internal + T_external >= T_hold

执行set_multicycle_path 0 -setup -to [get_ports DATAQ]之后,会相应地让hold relation变成T1到T0,这不make sense,

the hold check has to occur on the same edge, thus we need to

specify a multicycle of -1 (minus one) for hold check.

所以要执行set_multicycle_path -1 -hold -to [get_ports DATAQ]来告知tool正确的hold relation应该还是从T1到T1.

由于tool无法知道外部DFF的T_hold,只能假设为0,所以hold relation要求就变成了T_internal + T_external >= 0,

由于实际上DATAQ允许在clk上升沿之前的2ns内变化(可看成是T_internal<=-2ns),

通过要求 T_external最小为2ns来告知tool T_internal最小为-2ns:

set_output_delay -min +2.0 -clock CLK_STROBE [get_ports DATAQ]

与一般的时序比较,它有2点不同(相反的)

1)在clock的上升沿前后,不是一般要求的稳定时间,而是可以容许的不稳定时间,所以用的数值1ns,2ns也是反的

2)没有一个周期的延迟,所以用set_multicycle_path -setup 0, -hold -1 来处理

谢谢小编,关于您回答的第1点能否解释更详细一点呢?或者说我之前的解释是否有问题呢?

谢谢

主要是由于设置了一个虚假的muticyle 值(0), output_delay的数值是反的吧。 还望小编大人详解~