FLASH时序问题求助陈老大

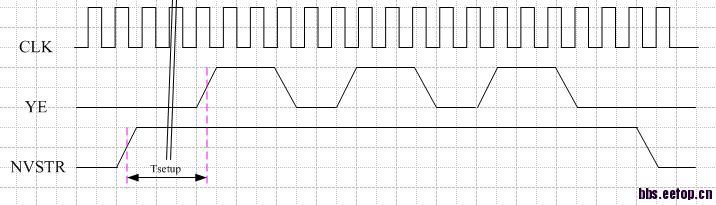

其中Tsetup的时序要求为10us。

这个是在我设计中通过基于CLK的counter来保证的。

NVSTR和YE均来源于CLK时钟域。

在STA时,无论我怎么设置(multicycle_path、false_path),均报Tsetup不满足要求

请教一下陈老大该如何解决这个问题

请把SDC和timing report贴出来

我在这里写一下吧,内网的东西,无法拷贝出来

SDC中时钟定义

create_clock[get_port CLK] -name CLK -period 48 -w {0 24}

对这条路径的约束试了一下几种情况:

1)set_multicycle_path 230 -from u_fcu/u_fl_uif/NVSTR_reg/CK -through u_fcu/u_flash/YE

2)set_false_path -from u_fcu/u_fl_uif/NVSTR_reg/CK -through u_fcu/u_flash/YE

下面是timing report:

StartPonit : u_fcu/u_fl_uif/NVSTR_reg

(rising edge-triggered flip-flop clocked by CLK)

EndPonit : u_fcu/u_flash

(rising edge-triggered data to data check clocked by CLK)

Path Group : CLK

Path Type : max

PointIncrPath

---------------------------------------------------------------------------

clock CLK (rise edge)0.0000

clock network delay (ideal)2.00002.0000

u_fcu/u_fl_uif/NVSTR_reg/CK0.00002.0000 r

u_fcu/u_fl_uif/NVSTR_reg/Q0.89472.8947 r

u_fcu/u_fl_uif/um_nvstr (net)0.00002.8947

u_fcu/u_fl_uif/um_nvstr (fl_uif)

………………

u_fcu/u_flash/NVSTR (FLASH32Kx16)0.00383.9697 r

data arrival time3.9697

clock CLK (rise edge)0.0000

clock network delay (ideal)2.00002.0000

clock uncertainty-0.40001.6000

u_fcu/u_fl_uif/YE_reg/CK0.00001.6000 r

u_fcu/u_fl_uif/YE_reg/Q0.85702.4570 r

u_fcu/u_fl_uif/um_ye (net)0.00002.4570

u_fcu/u_fl_uif/um_ye (fl_uif)

………………

u_fcu/u_flash/YE (FLASH32Kx16)0.00383.9513 r

data check setup time-10000.0000-9996.0488

data required time-9996.0488

------------------------------------------------------------------------------------

data required time-9996.0488

data arrival time-3.9697

------------------------------------------------------------------------------------

slack (VIOLATED)-10000.0186

试试

set_false_path -from u_fcu/u_fl_uif/NVSTR_reg/CK -to u_fcu/u_flash/NVSTR

set_false_path -from u_fcu/u_fl_uif/NVSTR_reg/CK -through u_fcu/u_flash/NVSTR

data check setup time-10000.0000-9996.0488

这个为啥这么大? 10ms ? 这么大,

看看.lib吧,flash里面有很多async path的,最好能看下文档

这个是SMIC18 chingis flash么,这么眼熟

非常感谢陈老大

的确解决了

10us,tsmc的flash

的确是这么大,FLASH program和erase时的时序要求

不过总感觉这个flash的lib文件很奇怪

flash本来是一个异步存储体,所以其输入到输出应该会存在具体的路径

但在STA时,所有through FLASH的路径到了FLASH的输入端都被认为是到了路径的终点

原来是tsmc的flash,

小编用chingis的flash IP啊?

chingis在流片厂商上好像有一些限制吧--至少不能在TSMC流片

不过据听说chingis的FLASH功耗做的比TSMC好很多

时序上就不是很了解了!

有没有相关的对比文件,给看一下

我做的smic18 chingis flash,

chingis 只是flash厂商,是在smic 做而已,

时序上有很多异步的path, 不用管的,

sdc里面很多false_path ,

tsmc是自己的flash还是别家的?

gsmc的是SST的,

TSMC是自己的FLASH,

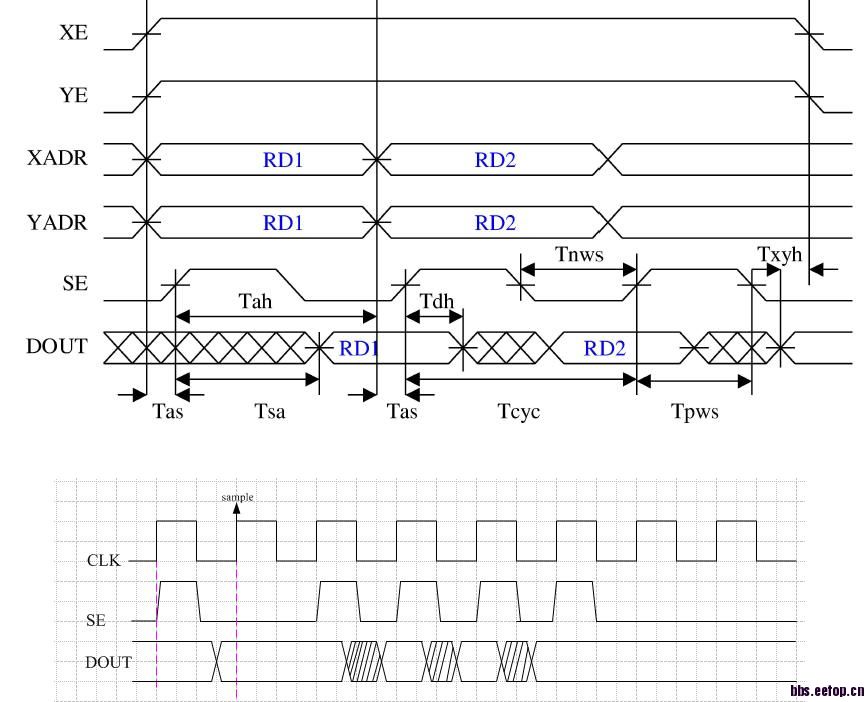

我纠结的是它的读操作时序,如下图

图片上半部分是FLASH的读时序

下面是我系统中产生的SE信号,按理说,在STA中,应该分析出SE有效至下一个时钟沿采样DOUT这条路径是否满足要求。

但由于FLASH lib的原因,

FLASH输入端全部被当做是路径的Endpiont。导致这条路径无法直接分析

很郁闷

flash输入端应该是做为 startpoint吧, 比如ADDR 这种,

你这个SE 是OE这种功能么, output enable,

SE是“Sense amplifier enable”

只有在读操作时才会用到这根信号

且这根信号是影响读时序的关键信号,只有在它有效以后,DOUT才会在制定时间输出

按照我的理解,FLASH的输入端应该是介于Startpoint和Endpoint之间的through点

tsmc flash,

个人认为这个timing model作的对设计非常不友好,用起来要做很多额外的设置

这个timing model更像是一个免责声明,而不是辅助用户设计的library

好高深哦受教啦~