芯片tape out出来后size扩大了200um

时间:10-02

整理:3721RD

点击:

大家好,我平时做电路设计,最近也画了一个版图。流片出来后,发现芯片的尺寸扩大了一点。

由于有特殊需要,希望芯片尺寸可以基本上自己算出来,所以请教如下,工艺是TSMC。

(我知道DRC rule里可能有相关的所有信息,但是DRC rule太长了看不完,自己又不是专门搞这个的)

流片回来,划片后某块芯片的尺寸是1268 X 1127。

Cadence版图芯片尺寸(以prBoundary为边界)再加上划片间距是1074 X 1095。

其中算划片间距是这样的:

我们有多个小设计拼版,芯片之间间隔100,确认过划片切刀是22,再加上两侧磨损,所以划刀计做30,

那么有划片的每一侧就加上 35。

现在和最终尺寸还有差距,其中一条边更是相差近200,这条边属于整体拼版的外围四条边(另一条边属于内部边)。

所以应该再加上seal ring和assembly isolation的20(DRC rule这样说的)

咨询了MPW的人说die saw应该再加40-80,那么按80算现在还差近100。

大家说说看还漏算了哪些制作过程,谢谢!

由于有特殊需要,希望芯片尺寸可以基本上自己算出来,所以请教如下,工艺是TSMC。

(我知道DRC rule里可能有相关的所有信息,但是DRC rule太长了看不完,自己又不是专门搞这个的)

流片回来,划片后某块芯片的尺寸是1268 X 1127。

Cadence版图芯片尺寸(以prBoundary为边界)再加上划片间距是1074 X 1095。

其中算划片间距是这样的:

我们有多个小设计拼版,芯片之间间隔100,确认过划片切刀是22,再加上两侧磨损,所以划刀计做30,

那么有划片的每一侧就加上 35。

现在和最终尺寸还有差距,其中一条边更是相差近200,这条边属于整体拼版的外围四条边(另一条边属于内部边)。

所以应该再加上seal ring和assembly isolation的20(DRC rule这样说的)

咨询了MPW的人说die saw应该再加40-80,那么按80算现在还差近100。

大家说说看还漏算了哪些制作过程,谢谢!

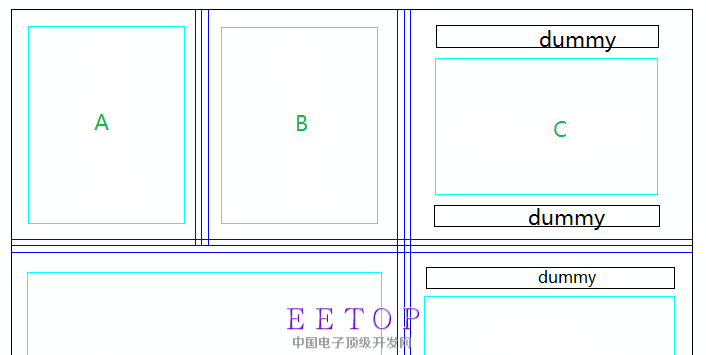

你说了是多个小芯片拼版,芯片大小是否不一致?

划片是按较大芯片来的,较小芯片四周加dummy与较大芯片面积保持一致,

那么较小芯片面积扩大了是可以应该的吧?

有没有shrink呀

没有shrink

整体拼版后,该芯片的占用面积是可以在cadence里量出来的(是在整体拼版的版图里测量),

我不太明白加dummy会导致加大是什么意思

芯片C上下加了dummy,与AB高度一致,划片后,芯片C的高度比实际大很多了

是不是 mask 都没有做对哦

MPW时,工厂没有给你们提供掩模数据,让你们确认?或者说Tapeout前都有相应的表格要填写。如果芯片大小不一致。最好还是像foundry确认。

Tapeout前都有相应的表格 => MT FORUM

multi die 最好排一长排比较好切割, 否则 DIE SAW 很容易毁其他 die . 至於 MPW 是一整块给你自己排吧 4000x4000or 5000x5000 .

layout die 画多少应该出来就多少 .

mask 那些 bias 只是光罩过程会使用 不会影响到 die 大小,除非是使用 非标准 shrink 工艺如 0.18 -> 0.13um,

但这类一般GDS shrink