版图中隔离管的作法(多衬底电位该如何处理)

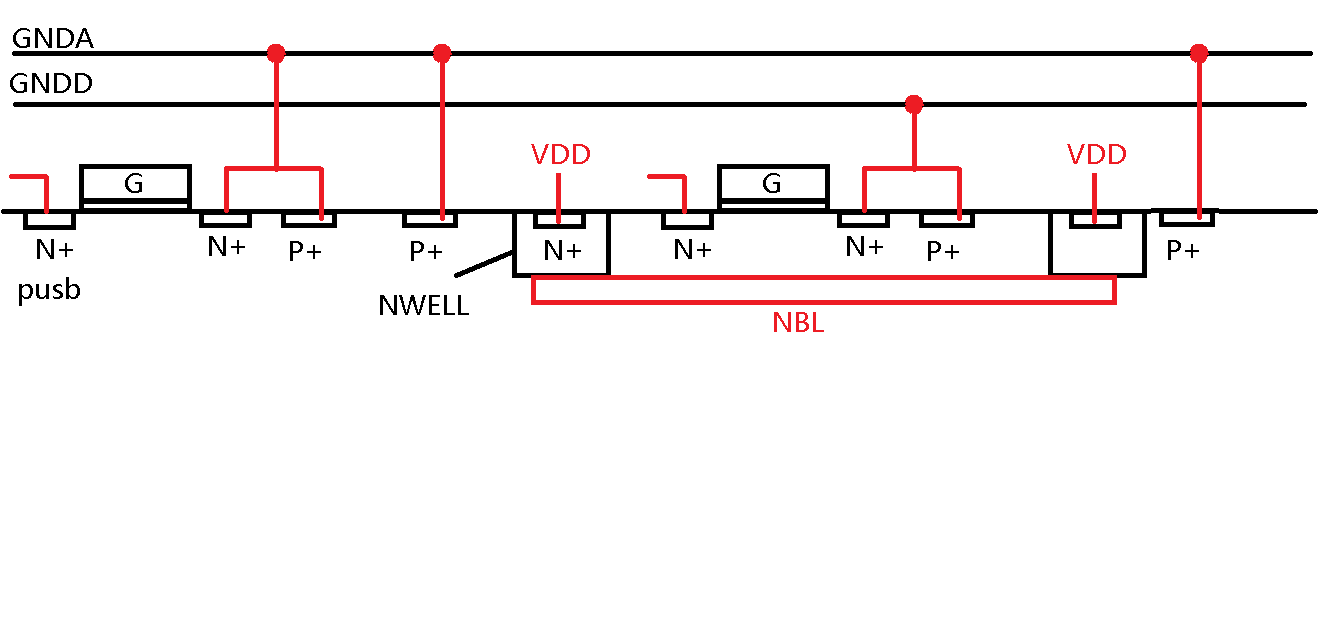

如果有DeepNwell是可以做的。

谢谢你的回答哦!如果有DNW的话,直接在VSS的NMOS区域画上一块就相当于是和GND的衬底隔离了,可以这样理解吗?

CSMC 0.5um不支持多衬底电位。一个比较器而已,何必要多衬底?

跟做P管类似,有个P阱或类似P阱的区域,在里面做NMOS,这个NMOS就有自己独立的衬底电位了。

谢谢你的回答哦!不支持的啊?好吧。这是一个师兄做的电路,我负责做版图的。那就没有其他解决办法了吗?

哦。明白了,谢谢你的回答哦!不过,四楼说csmc 0.5 不支持多衬底电位,哎。

我认为是你对电路的理解有问题,或者是你师兄胡搞。

是的,相当于做了一个隔离,不与psub接在一起了

谢谢!电路如何设计我倒不是特别清楚,老板安排的工作让做版图的。就是电路设计的时候NMOS衬底那块有VSS和GND两个电位了,所以做版图的时候有点纠结。

恩。明白了,非常感谢哦。只是我目前用的csmc 0.5um的工艺貌似没有DNW,比较难受了。老板也说做不了了。

那就是你师兄的问题了,如果他抄的是allen书上的电路,那么你完全可以把VSS变成0,GND变成3.3,原来的VDD再加3.3。电路的设计要根据工艺来的,先确定工艺才能做设计。所以你师兄肯定是在胡搞。

额,因为我师兄没做过版图啦,整个芯片都是他搭的,做电路设计的,可能他不是很清楚这个工艺库吧。恕我愚钝哦,如果VSS变成0,GND变成3.3V,VDD变成6.6V的话,那这样子不还是存在两个衬底电位么?

意思就是所有衬底接到VSS上。GND只是作为一个中间电位。另外,不懂版图是做不了电路设计的。

哦。明白了。谢谢啊!我现在在实验室帮着画版图,但我对电路设计也很感兴趣,现在不知道该先学什么了,您经验丰富,不知道能否给提点意见呢?谢谢了~

小编说有GND(0)和VSS(-3.3V),那你这个电路还能正常工作吗?衬底0V,suorce-3.3V,这个pn结早通了。

所以衬底要接到vss上。

因为存在多个衬底电位,一部分是接VSS另外一部分是接GND的,也就是相应的一部分NMOS source是接VSS另外一部分是接GND的。

关键是NMOS的第四端。有正负压的情况下。记得是去隔离SUB 接0的NMOS.然后DNWELL接最高电位。而不是去隔离-3.3V的。

谢谢你的回答哦!可是我不太明白,一是为什么要隔离接0的NMOS而不是-3.3V的,二是为什么DNWELL接最高电位呢,接最高电位的一般不都是PMOS的衬底么?求解哦~

学习中

一颗芯片不可能有两个不同电压的地

谢谢!电路如何设计我倒不是特别清楚,老板安排的工作让做版图的。就是电路设计的时候NMOS衬底那块有VSS和GND两个电位了,所以做版图的时候有点纠结。