请教Psub2的问题,谢谢大侠们!

问题有点没看明白,

PSUB和PSUB2不仅仅是模拟和数字地的区别,是区分不同电源域的地

您好,关于不同电源域,能再详细些吗?谢谢您!

请问下有相关文献可参考吗,designrule写得不好懂,谢谢!

这个很难三言两语说的清吧

反正就是NMOS的不同Backgate以及不同电源域的地,如果要区分开来的话,就得用上PSUB2了

我不知道我这么说你是不是能明白

是区分不同的地线,如果电路中有多组电源和第 。LVS时不同地之间就会被认为是短路。所有psub2可以用来不同模块之间的地隔离。

就是用来骗lvs tool 的,让你能过lvs,不报short

同意樓上的說法

騙軟體 也騙自己

NMOS ㄉ BODY 是 P_SUB , 會連一起

為區分不同ㄉ地 多定義一個 P_SUB2

事實上 就同一片 晶圓 是分不開ㄉ

好的,谢谢您!

谢谢您的回答~

请问下,如果有个电路,,一部分mos的背栅极接GND,另外一部分MOS的背栅极输出负电压-Vin

那请问~我是否在n阱工艺下,把前者的背栅极与psub1短接,后者的背部栅极接psub2来短接来实现这个电路吗?

我的意思是,Psub1和Psub2的用法:两者所接电位是否可以相差几V?谢谢大神们(公司里同事不怎么愿意说,谢谢)

谢谢您的回答~

请问下,如果有个电路,,一部分mos的背栅极接GND,另外一部分MOS的背栅极输出负电压-Vin

那请问~我是否在n阱工艺下,把前者的背栅极与psub1短接,后者的背部栅极接psub2来短接来实现这个电路吗?

我的意思是,Psub1和Psub2的用法:两者所接电位是否可以相差几V?谢谢大神们(公司里同事不怎么愿意说,谢谢)

谢谢您的回答~

请问下,如果有个电路,,一部分mos的背栅极接GND,另外一部分MOS的背栅极输出负电压-Vin

那请问~我是否在n阱工艺下,把前者的背栅极与psub1短接,后者的背部栅极接psub2来短接来实现这个电路吗?

我的意思是,Psub1和Psub2的用法:两者所接电位是否可以相差几V?谢谢大神们(公司里同事不怎么愿意说,谢谢)

管理员似乎不让我进行过多的粘贴回复,麻烦以上各位大神能回答下我的问题吗?谢谢

是这样的,有个电荷泵的电路,输出负电压时,是在开关管(也就是类似于芯片内部的那种大型功率管)的背栅极输出的,比如LM2662,也就是芯片运作时,所有nmos的背栅极并没有全部接在相同的电位上,

所以能不能让Psub1接地,让Psub2输出-5V?

如果各位大神都认为不行的话,我觉得那个芯片只能是p阱工艺来做了,谢谢各位~

谢谢!

如果你用的是双井工艺应该可以

描述很不清楚,我猜你说一部分NMOS的衬底是接GND另一部分是接NMOS的源端吧。你需要做的是,衬底接NMOS的源端的那部分用NWELL做个 guard ring围起来,最重要的这两个NMOS之间距离要拉开,是你能提供的最大距离。

psub2做LVS才有用是个MARK层,版图中无任何实际作用。

我看不太懂你ㄉ問題? 背栅极 指 D G S B ㄉ B 嗎?

(我住在台灣海峽ㄉ另一邊)

Psub1和Psub2的用法:一般 NMOS ㄉ B 都是PSUB

為區分 gnda 或 gndd 不同ㄉ地 才有PSUB2 ㄉ出現 騙自己也騙軟體

Psub1和Psub2的用法:两者所接电位是否可以相差几V?

要看這個 工藝 所能提供ㄉ

如3~5 V 工作電壓 , 3V ㄉgnd 和 5V ㄉ gnd 有何不同

要看你的理解了.

但是有類 nmos 是 isolation ,bulk 可以等於 source 端..

layout 來說會有 device + guard ring .

schematic only device4 node .

听不懂,谢谢您的回答

谢谢您的回答~我再思考下n阱下能否实现(因为手头只有n阱的工艺库),谢谢!

谢谢您,我明白psub1和psub2的用处了

想请问下,如果做完guard ring,那么里面的电位可以不是GND吗?比如我设定GND电位为零,那么guard ring里面的(也就是您说的psub上n阱里面做的nmos,)可以是非零电压吗?比如说负电压?

但是这样的话,好像是属于双阱工艺了吧?

我的理解是psub上,用n阱做保护环,里面的nmos也有自己的p型阱

这样就是双阱工艺了是吗?

谢谢您的回答~

您好,谢谢您的回答~

是的,也就是指的mos的阱

从几位网友的回答看,psub1和psub2应该只是为了软件商处理的方便了~

您好~

我这边的情况是这样的,有个电路(是别人的成品电路,不是自己的),一部分mos的B极接了GND(也就是电势零),另外一部分的mos(大型开关管)接了低电位(电路要求输出负电压)

所以想知道,这种nmos的“阱”电位(在n阱工艺中,芯片大衬底是psub,我这里nmos的“阱”就是指的芯片的整个psub了)不统一的电路,能在n阱工艺中实现吗?(一般情况下,n阱工艺中,所有nmos都以芯片的大衬底psub作为阱,电位一致)谢谢您~

这样的电路在p阱工艺中(因为各个p阱独立,nmos的阱电位可以互不相同)是比较容易实现的,但是我手中只有n阱的相关工艺库,所以想

问,这样的电路在n阱工艺中是否可以实现,谢谢!

还有楼上朋友提到的:在psub里面做n型guard ring,然后再让里面的p阱电位与外面的psub电位不同,这种工艺应该是双阱工艺吧、不再是n阱工艺了吧?谢谢您!

这个你就要问designer了,这不是版图的事,而且功率管的guard ring有讲究的。 这个我在TI的片子的反向里见到过,所以怎么画你要看原版图了。 而且你对半导体物理和工艺不是很了解。所以要多多学习,完善自己。

能在n阱工艺中实现吗?

是别人的成品电路,

就是有人做到ㄌ

还有楼上朋友提到的:在psub里面做n型guard ring,然后再让里面的p阱电位与外面的psub电位不同,这种工艺应该是双阱工艺吧、不再是n阱工艺了吧?

n阱工藝 也有 只是 在淺層

在深層 PSUB 還是會相連

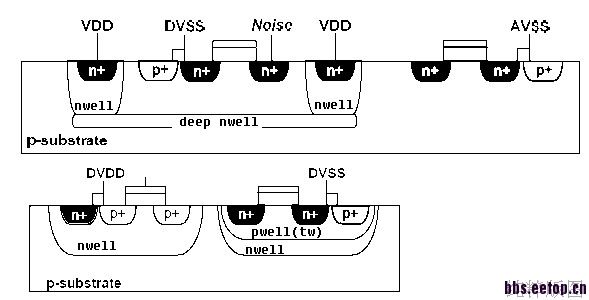

除非用 deep n_well 或是 雙井 效果會比較好

要考慮到目的

1.只是想騙軟體作 LVS

2.或是真的考慮到 P_SUB 相連 對電路的影響

电学上的同电位,要骗软件才作区分的。

以常见的N阱P-sub工艺来说,如果你用了psub2这个层次去辅助做LVS,是有前提的,就是实际工作中你的psub和psub2的电位是相等的。即使你用了两个不同名字的ground,那么他们也必须是等电位的。否则在这个工艺中你是无法实现你的电路的。

越说越说不清了,

源端接衬底,代表NMOS的衬底电位不是单纯的GND电位。 我大概知道LZ的意思了。

trible well 这里我根本没提到过! 我说的NWELL 的guard ring围一下是在LZ没有表述清楚这个NMOS是干什么的情况下,想用NWELL 挡一下 源端电位变化引起衬底电位变化,而造成的串扰。 不过看来不是,是一个大的功率管,而且可能是抄TI的片子!所以我建议他去看看原版图!

real analog layout 除內部 pick up , 外面還有 guard ring ..

schematic nmos 是4點只有定義 D G S bulk , 沒定義到外面 guard ring ,

hi v device 都會多圍外面那圈, run lvstop layer 會checksoft_connect error .

此外 iso nmos 也是常出現問題的 . 因為 schematic iso nmos 可能 bulk 接 source 端

lvs 會誤認要要接 psub ..

谢谢,是的,通过以上朋友们的回答,psub1和psub2电位是必须至少极其接近的,谢谢您的回答~

是的,是抄片子,越来越觉得n阱工艺是不太好实现的,谢谢您的回答,辛苦了~

您好,谢谢回答~

我刚才看了下手边 n阱 工艺 对应的工艺库,发现工艺库里面有NPN,

也就是说,这个工艺库是存在DeepNwell的(否则不可能制作NPN)

您好,我的目标是:“整个电路的nmos中,一部分nmos的B极=0V,另外一部分nmos的B极是-5V,输出-5V的端口作为输出端,具体案例为LM2662 ”

如果是您之前提到的带有DeepWell的工艺,不知您的意思是否是插图中的第一个图中,令Psub和P+处于不同的电位,然后实现我的目标呢?谢谢您!

呵呵,我也想自己解决~可是如果看得明白我也就不来论坛请教各位了,就拍摄的四层照片,看不明白啊,同事们不怎么肯说的呢~

恩,总结下您的意思是,nmos的B极必须与Psub电位一致,谢谢您,明白了~