为什么有的poly电阻layout上面用M1覆盖着啊?

一般建议电阻上不要用M1走线,会对电阻产生影响。那么如果都加上M1就可以保护起来。个人理解,不知道是否正确。

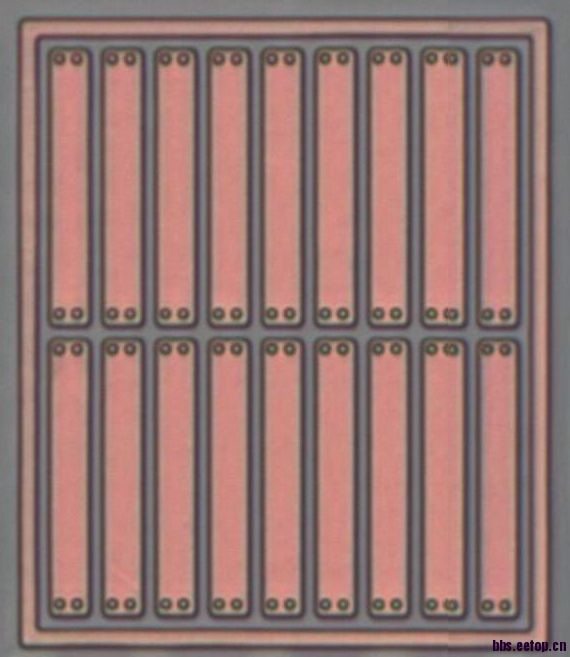

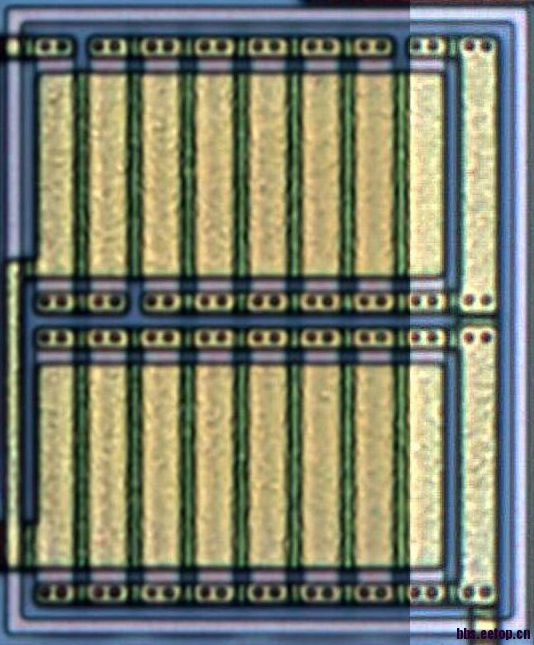

POLY电阻上加M1,那时屏蔽层,起到保护电阻体区的作用,使阻值更精确。

不过M1通常看到的都是floating的做法

原来是接地的效果更好吗?求解看來是做 屏蔽的

有接電位 會比較好

乾淨的 ( vdd gnd )

最好可能是人家做着fib用

看不懂

3楼的说的有理,是屏蔽用的。你可以放心的在电阻体上走线了。

同轴线的原理,屏蔽重要信号。貌似不为了在电阻上走线。而是电阻里面走的信号很重要。

电阻的阻值受电压偏置影响,在电阻上覆盖一层接地的m1,进行屏蔽保护,以免电阻阻值变化

Poly电阻上是否加屏蔽层M1金属,如何判断?见CSMC中rule建议poly电阻上加M1保护,但SMIC、TSMC中rule没有说明,求tsmc、smic中电阻是否加屏蔽层M1?

因为器件在刻蚀的时候是处在一个强电场的环境中,这个环境中存在很多静电,之所以加个M1盖在电阻上是将静电吸收,然后再导入地!

还有一个原因是从氢化的角度来讲的!metal1和电阻周围的G-ring同电位,电阻好像被一圈同电位的包围起来,起到静电屏蔽的作用;坛子里还有人说过fab建议盖满metal1可以防止氢化对电阻上离子浓度的影响。

那请问在电阻上直接加满了metal 1 不会导致在刻蚀metal 1时 氢化更加严重 啊,求解!(不是说电阻上不要走线就是为了防止氢化的影响啊)

这个我也很疑惑,没讲清楚,而且常用的UMC/TSMC design rule里也没有这条attention。

如果电阻排列后面积占得很大,电阻上盖metal1也可以解决电阻区域metal1的density问题呀

隔离噪声吧

如果在poly上面加金属作为屏蔽,那么除了m1之外,其他金属行不行呢,有什么影响吗