rf电阻的第三端接什么电位

时间:10-02

整理:3721RD

点击:

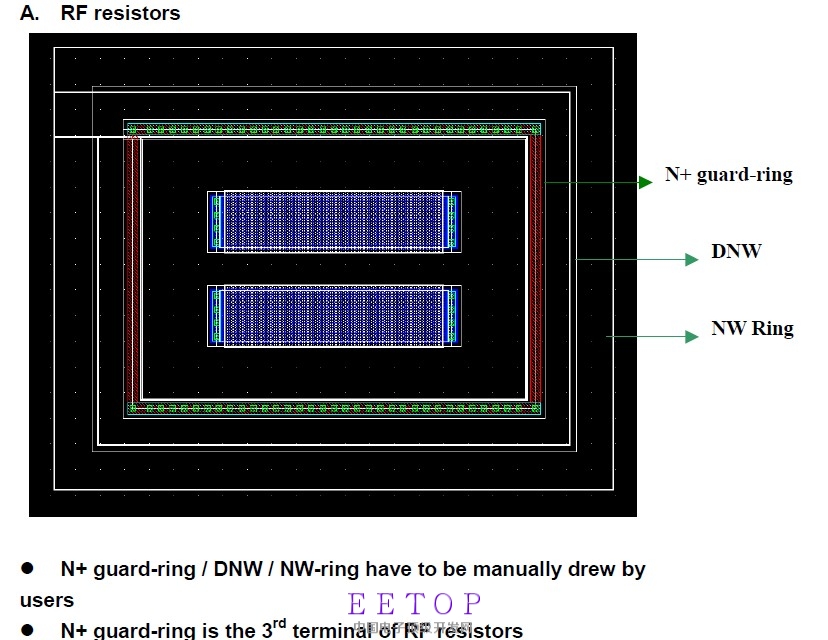

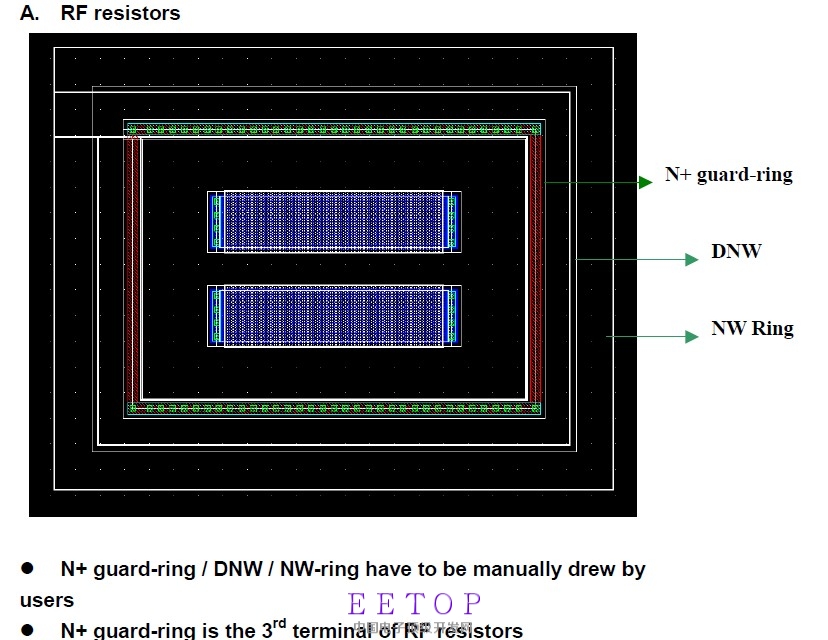

电路图中第三端接的应该是gnd。但说明文档给出的图显示,n+gardring是第三端,所以,版图上第三端接的不应该是vdd吗?这样才能形成反向pn结起到隔离作用。请问电路、版图的第三端究竟要接什么电位,恳请指点!

看线路要求接地也是可以的

电阻放在PW中,用P+ring 围起来,是不是可以?

请问是电路接地还是版图接地呢?原理是什么?

这个电阻应该是rf nwell 电阻,要求必须第三段接Nring 电位,应该是电路设计接错, 或者还有一种rf pwell 电阻.如果把这个第三段接GND, 你的DNW 和GND 可能会short.

一般来说,如果是well(P/N)电阻、diff电阻等有源电阻,所在well需要避免结的順偏漏电。如果是poly电阻,poly与下方的well不会存在直接的通过,well电位相对较灵活一些,面积比较充分的情况下,可以考虑将poly电阻放在nwell里面,有隔离噪声的作用。至于well电位,建议nwell接到相对稳定的高电位,若接到低电位或多或少有latch的风险,pwell的话接到低电位就好。此外,若是高压环境,注意寄生MOS的影响。

在看陈诚颖的coms模拟集成电路设计中,第七章lna也是rf电阻第三端接的地。所以我现在很混乱,难道电路第三端和版图第三端接的不是同一电位?

我也觉得nwell应该接高电位,但书上确实接的地,不太理解。

接地也不是说不可以,相对来说地上的噪声比电源可能要小吧。只是nwell接地,要特别注意周围的环境,避免foward or latch,有些fab的rule就会要求0V的nwell要和接电源的nwell拉开40um!

这个关键是要看你的制程,如果有负压,nwell 接0V 其实也是正电压. 关键是制程,研究下制程剖面图吧!

PSUBOR nwell