关于版图中NMOS、PMOS衬底接法的问题

本人新手,最近在实验室别学边画版图,遇到一些问题,不太明白,特来请教下论坛里的大神们,望指点一下。

我是先设计了电路图,然后APR自动生成的。在电路图里,PMOS的衬底都是接源极,都拉到VDD(3.3V)上去了,但是NMOS的衬底有一部分是接到VSS(-3.3V)上,另一部分是接到GND(0)上去的。然后画版图的时候问题就来了。PMOS的话我是用body type给接到VDD上去了,但是NMOS的衬底我没给画,然后就都报错missing connection。但是,我之前也画过几个版图,同样是APR的,但是电路图中NMOS的衬底只接到一个电位,非GND即VSS,所以,那时我只画了PMOS的body type(因为没画的话LVS的时候会报错),没画NMOS的body type,LVS能通过,但是现在就不行了。

我是这么想的,因为PMOS是做在独立的N-well里,所以它必须接源极,接body type,而NMOS是做在p-subtract上,所以他们要接公共电位。所以,当电路中只有一个电位,即VSS或者GND的时候,可以不画NMOS的衬底,但是如果存在多个的话就必须要画出来,是这样子吗?

对于这个问题比较模糊,望大神给我解答一下。谢谢啦!

我用的是CSMC 0.5um的工艺。

刚刚我把其中一个NMOS的body type接到VSS上去以后又报了一个新的警告。

WARNING : stamping conflict in SCONNECT - Multiole source nets stamp one target net.

看不太明白,有没有大神可以给我解释一下么。谢谢啦!

Psub只能有一个电位。

你现在的接法很明显出现了两个不同的Psub电位,当然会报soft connect的error。

你的NMOS确定都是做在psub上的?

谢谢你的回答哦!了解了一些,但是,既然电路中有两个psub电位,该如何处理呢?改电路吗莫非?另外,单psub电位的时候我NMOS衬底没画,为什么LVS也能通过?这是我想不通的地方。

我是电路图中,直接tools-design synthesis-layout XL过来的。

一 两个psub电位,接GND(0)的管子可以直接放在称底上,而接(-3.3v)的管子可以作成隔离管,把称底隔离起来就不会出现软连接的错误了。

二 单称底的时候 NMOS不画称底接触,不表示真的没有称底接触,因为整个称底是一个整体 ,即使很远的地方有个接触孔,也是默认NMOS 有称底接触的,所以不报错。

以上个人的看法,期待高手指正

谢谢你的回答哦!对于第二点,我也是这么想的。明白了一些,得回去看看隔离管的内容了。

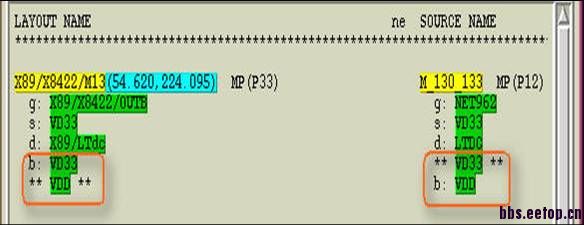

您好!我可以问你个问题么?图片中的b:VD33和**VDD**之类的该怎么理解呢。还有就是,像X89/X8422/M13(54.620,224.095)这一串是什么啊?新手刚进实验室,不太明白,还请指点一下,谢谢啦!

LVS仿真报错

1 管子的称底接错了,电路是VDD而版图接到了VD33上

2X89/X8422/M13(54.620,224.095) 指的是layout上出错的位置坐标

谢谢哦!还有一个就是我不明白的是X89/X8422具体代表什么含义呢?这个也不是器件的名字啊。

层次化的信息。比如我的某个顶层电路cell 是I1(cell的instanceName),里面有个小模块cell 是X2,X2模块里面有个MOS管是M3(举个例子),现在这个管子有错误,那么报出来就是I1/X2/M3,你可以再去对照你的电路看看。顺便回答下你上面的问题,P管就不说了,N管的话,一般咱们就一个低电位(GND),像你这种有两种低电位的,有一种N管就必须做成隔离管,拥有单独的衬底。版图上有PUB2层,用PUB2可以画另一种衬底,因为没具体遇到过,我只能这样给你说一下,了解一下吧。

谢谢你的回答哦!非常感谢你的解释以及指点,又明白了不少东西。我得去研究一下如何画隔离管了。顺便好奇一下啊,大神们现在做模拟版图都是手工画的还是APR生成单元再画的呢~

电路可以直接转为版图么?小编用的是哪个版本的cadence?

不是直接转化为版图,是把电路图里的器件转换到版图里,每一个MOS管都是一个版图单元,然后自己连线就好了。

APR应该是自动布局,如果是那些数字电路,这个没问题。你要是画差分对,电流源这些对匹配要求高的电路,应该还是要手画的。

一般的一个电路,如果有两种地,有两个情况:1,数字地和模拟地。这种情况下虽然有两个地,但实际上都是连到psub 上的,只是希望在片外连,或者顶层连,作用是避免数字地的噪声影响比较安静的模拟地。所以他们实际上是连一个电位,只是在你当前层作为两个信号分开。这种情况可以在其中一种地的区域加上PSUB2这层,LVS里面就不会报错。

2,两种不同电位的地。像你说的,一个接0一个接-3.3,那么他们实际不能连接在一起。所以其中一个你就需要把它放在Deep Nwell里面。这样就可以形成pwell,以区别psub电位。

你的layout会产生gds,它里面有类似netlist的信息,这也是为什么可以做lvs.你layout里面的管子它也会给你标名字,X89/X8422这个就是在x89这个模块里面的x8422这个器件。在这句话的左边应该对应有netlist里面的器件名字。

非常感谢你详细的回答!明白了不少东西了。作为layout新手,还有很多不懂得的地方,正在慢慢学习,感觉有这么一个论坛,可以交流学习,真的挺好的。

同是新人,学习一下

受教了!

很明显你电路上就是有两种不同电位的NMOS,而你接在同一个电位上,那肯定会报错,两个地,好像还要加一层电源识别层以区分两个不同的地

学习了