mim电容因天线效应发生击穿问题探讨

时间:10-02

整理:3721RD

点击:

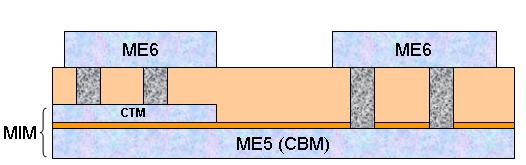

如图,这个MIM电容上下极板都用到ME6,ME6就是TOP metal,CTM为上极板,CBM是下极板。

为防止刻蚀过程因antenna引起电容击穿,design rule 规定0.5<T/B<2,T:T是上极板ME6的面积,B是下极板ME6的面积.

那么问题来了,电路设计把下极板接GND,在CHIP级,GND 用了大量的ME6,T/B<<0.5,过不了验证,工艺商给的建议是在上下极板接一个diode,只是理想的认为ME6上过多的电荷会通过diode泄放掉,没有designrule 可以检查,也没有说100%能行。

请问工艺商给的建议是否合理,如果合理,为什么电荷优先从diode流过?

你这个是TSMC的工艺吧!按工艺说的加上dio是没有风险的。我们已经很多次流片实验了。至于电荷积累多了,dio就会反向击穿,从而不至于烧毁介质层

为什么会有0.5<T/B<2的要求?

同问,大于0.5 理解不了····

罐罐水请理解,嘿嘿~

0,5<T/B<2,上下极板的面积比,目测是考虑在光刻的时候,上下极板都会累积电荷,电荷的多少取决于金属面积,在电容那个位置会有电势差,如果电势差过大,会把电容的介质击穿。所以这条rule是合理的,问题是加个diode能解决问题吗

金属积累的是电子,diode达到导通条件后电子都泄放到sub 去了。

加Diode应该是没问题的

上下极板累积的电荷会会形成电势差,在diode被击穿前,那个电势差会不会先把电容介质击穿?你们也是凭感觉加的diode,没有rule可以检查通过?

积累的电荷是先击穿电容还是击穿diode?能不能给个理由

我也不知道具体工艺哈,一般普通工艺单位容值1fF的mim大概击穿电压在十几v左右,这个值design rule上一般会有。diode的击穿一般会小于10V,所以大概能起到作用。

上面都是大概值,具体行不行还是得看工艺。

大概就是这样了,谢谢你的回答!

没有用过T的工艺。如果是为了防止ESD的话,这个Diode应该是正向连接;

我不知道T工艺中MIM电容的击穿电压是多少,但是应该是比Diode的反向击穿电压要高。