多晶硅栅做导线用有什么弊端

时间:10-02

整理:3721RD

点击:

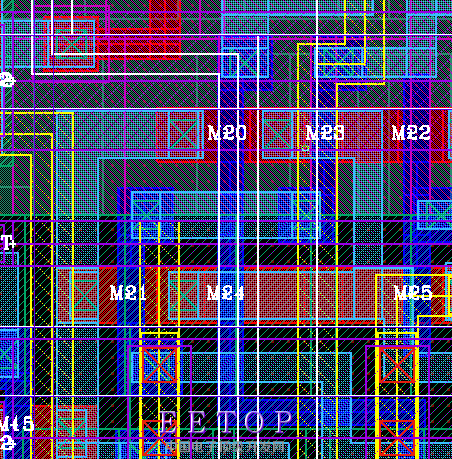

多晶硅栅做导线用有什么弊端,如图中M21、M23,总感觉这么做不合适,请大神赐教!

貌似连得也可以,不过一般不把mos管g极两头打孔做走线用

电阻大啊,所以要尽量短。

如果必须要走线的话不要太细,也不能太宽,不然电容会很大。

只在标准单元里见这种连接多些,因为对于金属层要求比较严格,有可能有走不开的情况。

模拟一般不这么搞吧,连线电阻会很大,电容也大,前后仿会差很远---

电阻和电容会有影响,对频率要求不高的话poly是可以适当走线的,mos gate poly 确实一般不2端打孔,会有弊端

恩 多谢大家的点评!

数位的没有多大影响 要是 模拟就不行 poly 一个方块的电阻值很大

poly要尽量短,因其电阻很大,不过要是size要求很严又没有多层metal的情况下,数字部分是可以用poly连线的