请教一个MIM电容的问题

图一是MIM电容整体模样,图二是打散后各层次模样,有四层,分别为:M3,M4,MMC,VIA3,图四是VIA3

我疑惑的是,电容用M3 和 M4制成的,上面打上VIA3这样不就是上下级版短接了吗?这样的电容怎么工作?

ps 这不是备用电容

你这问题我也是醉了。看来layout上的金属都不能相交了,因为一打via它们就短接了,这样的IC能有什么用?

相邻金属打上通孔难道不是短接吗?(M4 和M3打上VIA3)

谁叫你直接在上面打孔了?

M3,M4,MMC,VIA3 在这个时候,MMC类似于金属,此时VIA3是连接MMC和M4的,VIA3并没有穿过MMC层到M3,而真正的电容是M3和MMC的,

工艺要求是这样做,所以我才纳闷啊

谢谢解答另外再冒昧问问,工艺上是怎样控制via不穿过mmc到达M3层的,因为其他via3都是这样的目的,而电容上面的via3为什么单独不行?

建议小编问工厂要一份MIM的剖面图,或许就会明白了。

同意樓上的說法

这个你就得问Fab了,

我都没有权限跟fab联系MMC工艺文档里是怎么描述的?

那你好好把Design Rule中MIM的内容看看,应该会有说明,比如会提到哪层作为上极板,哪层作为下极板。

哈哈哈

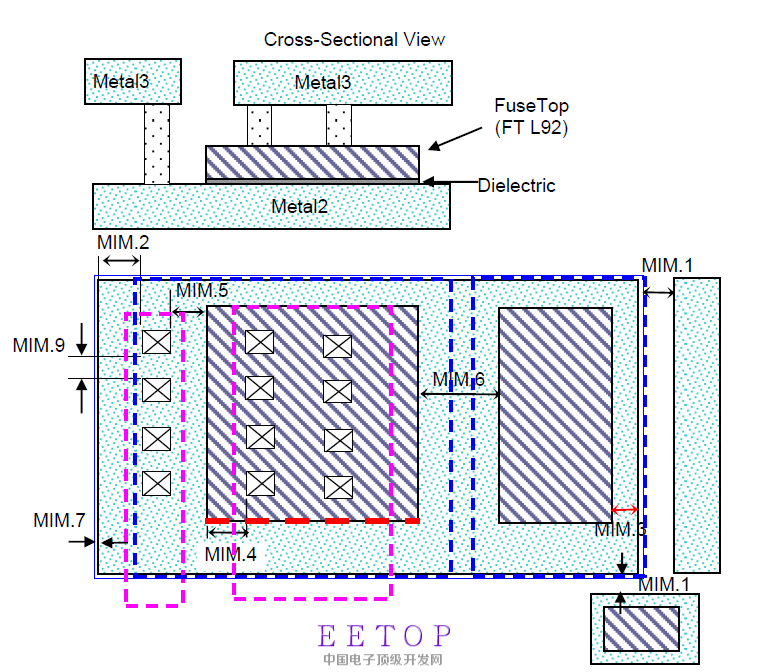

看下这个剖面图就知道是咋回事了,这里的FUSETOP就是你的MMC层,左边的没有MMC这层,M3经过V2孔流入M2,这样就连接起来了,但是右边M3通过V2孔到了FUSETOP层,并没有到M2层,所以M3和M2并没有短接!

看下这个剖面图就知道是咋回事了,这里的FUSETOP就是你的MMC层,左边的没有MMC这层,M3经过V2孔流入M2,这样就连接起来了,但是右边M3通过V2孔到了FUSETOP层,并没有到M2层,所以M3和M2并没有短接!

为什么这里图片没发上去,图片见楼下!

谢谢你解答,看到这里我有个疑问。这里有FUSETOP(即我说的MMC)的地方,via孔没有那么深,所以电容的上下极板没有连接起来。那么问题是,同一批次的via孔同一时间制作,怎么保证有FUSETOP 的地方via孔就做的浅一些呢?另外,增加via把M3和FUSETOP连接起来的作用是什么?请教了,谢谢

这个问题常有人问,这个帖子也有一些天了,看了看大家的解释,说法本身都是正确的,但是似乎没有正面回答小编的问题。在这里把我的一些浅见给大家说一下,供大家参考。

说起来简单,fab在做via的刻蚀的时候,控制的不是深度,而是材料。

层间介质是SiO2,电容的下极板表面是TiN,可以认为是一种金属,在选择via的刻蚀液的时候,选择可以只跟SiO2起反应的,这样在遇到金属层(无论是下层metal还是mim电容的上极板)的时候,反应即停止,这样看剖面图的时候,via的深度是不一样的。当然实际上会复杂的多,例如会加入时间控制等等。

请注意刻蚀时控制的不是深度,请大家再想一想,PIP电容,不同metal层次的开窗,这里的contact和pad,其实都是同这个via一样的原理。

2015年的最后一天了,祝大家新年快乐,心想事成。新年快乐!谢谢你的解答,我明白了。祝工作顺利

感謝分享