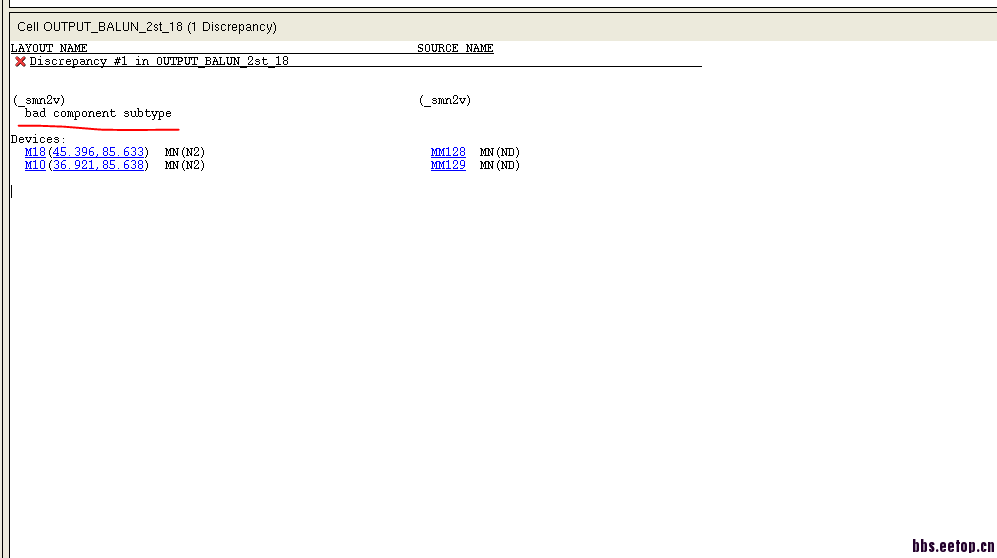

T18工艺 LVS报错: bad component subtype

[attachimg]615510[/attachimg

[attachimg]615510[/attachimg后来在calibre LVS rule文件里发现下面语句:

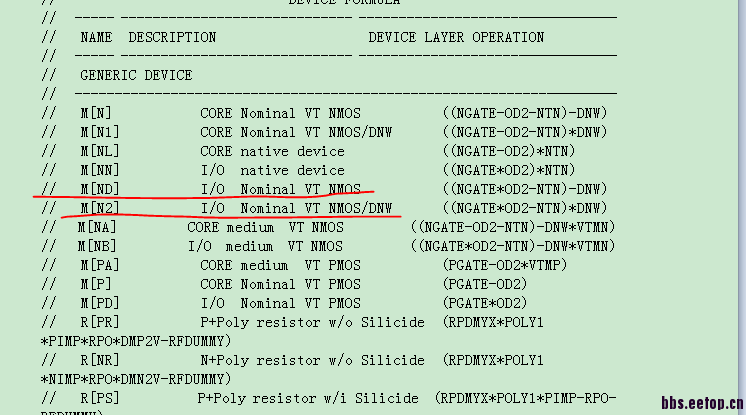

在calibre中layout中识别的是N2模型,而原理图中是ND模型,我觉得原因在这里,想知道该怎么修改rule文件来通过LVS,谢谢各位!

很明显,N2和ND之间的差别就是有无DNW,

既然电路没错,版图又存在DNW,只能说明版图错了。

要么改电路,要么改版图,不要怪责工具

谢谢啊!我说一下具体的情况

因为电路里面有两套地,所以每个模块单独过LVS时,都通过了,包括着一部分,后来把各个模块组装起来,一起过LVS,由于有出现两个地,所以使用了深N阱做隔离,在原来的版图上只是加了深N阱,其余的并没有变,但是LVS就是不通过;

我在想是不是深N阱加的有问题。

你说的深N阱就是2楼说的DNW。所以你明白了没……

啰嗦地解释一下:

本来你两个模块都通过了。原本也确实是ND的。然后为了分开两个地,你加了DNW。ND果断变成N2了。你应该超级感谢LVS抓到了你的错误。

我非常不理解的就是,你为啥会觉得在版图上加个新层次不会影响LVS?

同意樓上的說法

T 晶圓代工 通常用 PSUB2 來區隔不同地

只显示一下DNW那层,看看你所隔离的两个地是否真的全部隔离开?有没有包完整?整体LVS有没有关于地混淆而出现的错误?如果没有的话,那你就好好看一下你的rule关于N2和ND的详细定义。

DNW画得有问题啦

既然说到分隔地的问题,忍不住多聊两句。这绝对是个杀死新手的大问题,一不小心就是毁灭性的错误。我当初也被耳提面命地教育过很久……

首先,设计出两个(或更多)地,是有不同目的的。有的虽然名字不一样,但最终电位是一个;有的根本就不是一个电位。同个电位的还好,不同电位的如果没能隔离是要死片子的。

其次,DNW和PSUB2对于隔离地,完全是不一样的工艺。DNW是物理上彻底隔离,两个地之间被完全分隔,绝对不会短路(只要你别做错)。PSUB2是“虚的”,根本不会有这么一个层次出现在真正的芯片上,这个层次就是用来完成LVS的任务而已。

所以,PSUB2是具有很大风险的。你用DNW,出了错,这是好事,因为它替你把了一道关。用PSUB2,根本就不会报错,你会妥妥地跑过LVS,然后就碰运气看这两个地到底会不会因为短路死给你看。

我在很多不同客户那里都接到要求说“你给我把所有NMOS的区域都包上PSUB2”,虽然我完全符合要求地做了,但是我真的觉得他们是在作死……为了不让作死变成真死,我还得非常小心地把所有PSUB2高亮,肉眼观看一遍。

8#说得很好,赞一个。

DNW我也是碰到过,PSUB2没有遇到过。

8楼说的对,小编你太相信模块的lvs了,顶层出问题你改rule,对了又能怎样?

SCH上面用的是ND还是N2?衬底最终的电位到底是不是GND,还是DYNAMIC的,不要怀疑RULE,要怀疑电路

首先你们要搞清楚 如果你的版图里用到了PSUB2那都是底层的block里用到的,有的时候是为了把一些管子单独做一个衬底,减小和其他部分的寄生,但是到顶层最后还是一个地,所以说用PSUB2骗lvs的话不能这样讲,这么说是错的