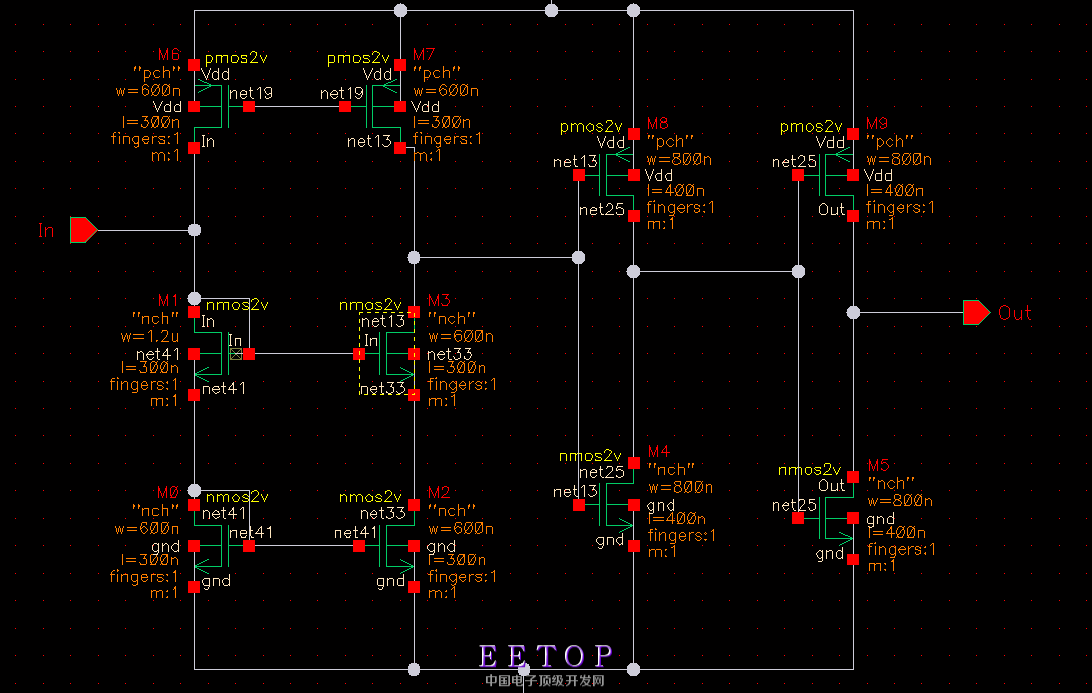

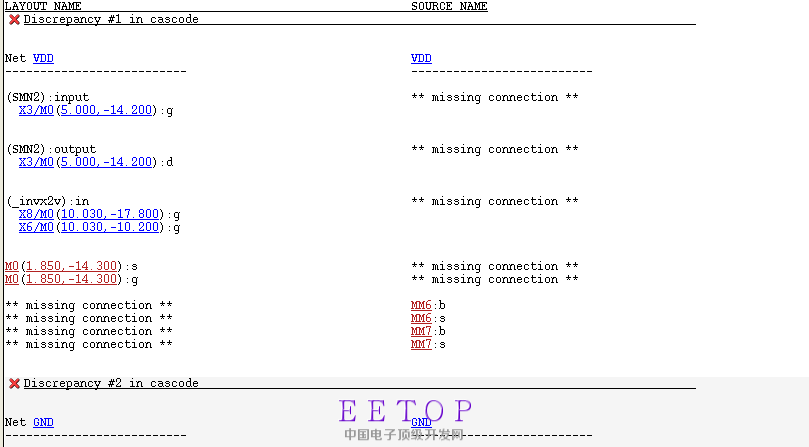

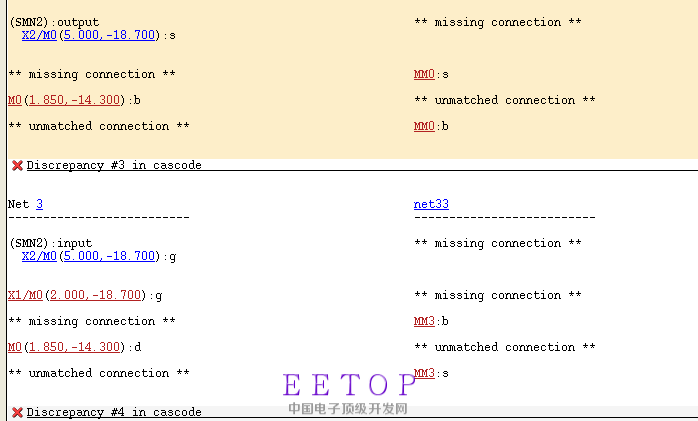

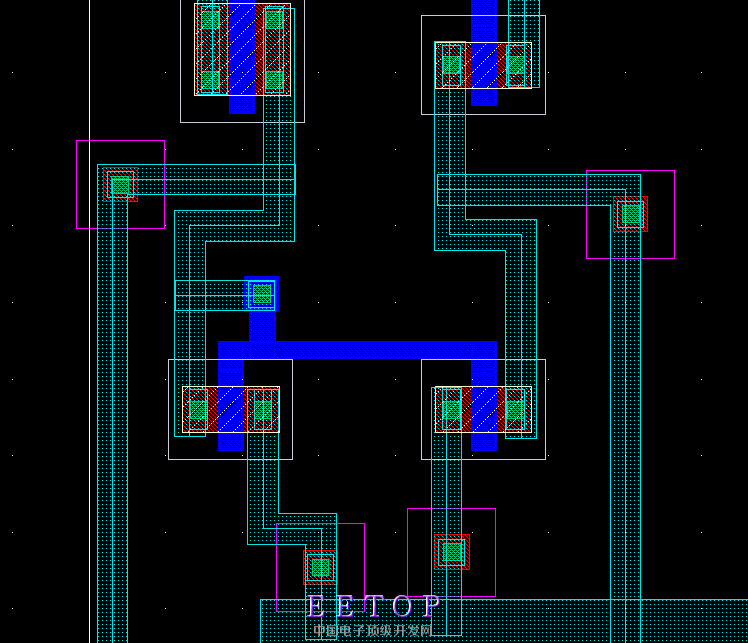

IC5141 layout LVS报错,求助大神。

你DRC跑过没?

跑了 过了,只有覆盖率的几个选项没过。

哥们,你的M1/M3的衬底端接的不是gnd啊,这样肯定会错的

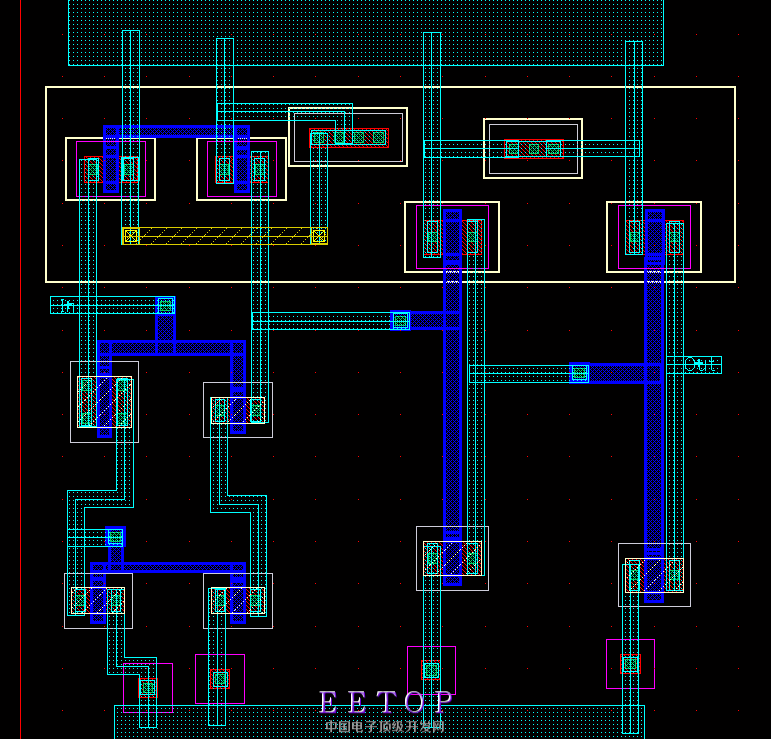

谢谢你的回复,我该怎么接呢,我是小白,还望指教下,这样可以吗?

要看你是什么工艺,如果你工艺有DNW这层,那么可以把所有的n管放在dnw里面,然后M1/M3放在一起,单独外面包一圈NW,这个形成PW(hot pw)这样就可以了,没有这个dnw,就需要使用PSUB2这个层次把M1/M3包起来,这样LVS是过得,但是物理上M1/M3和其他N管其实还是通过衬底软连接在一起的,但是由于一般衬底的电阻超大,这种软连接可能实际对你电路性能并不会有多大影响,但是不建议这种方法,最好放在DNW(深阱)里面

M1/M3衬底不需接地,电路接的信号线,你要根据电路接,前面的版图是衬底没有接所以会报错的。

你的M1M3衬底电位是独立的,都不是gnd,放两个PSUB2层次包起来,两个PSUB2区域的电位分别是两个N管的source端电位,这种放大不建议,PSUB2是为了配合lvs存在的层次,物理上不做这个层,所以其实物理上这两个管子还是和gnd软连接的,但是呢,由于衬底的电阻非常大,所以其实性能不会有很大影响;第二种方法是引用dnw这个层次,把所有的n管放在dnw里面,分别用单独的nw把M1、M3包起来,这样每个当初的nw中间挖空放nmos的区域就是单独的pw(可以不是gnd电位),这才是这种管子的最正确处理方式。没有DNW(深阱)就只能用PSUB2了吧

你的电路 M1 M3 衬底端没有接GND 你的layout画法相当于接gnd了 如果想让lvs 过 要么改电路让接地要么改layout 让M1 M3衬底分别接其S端

其实错误不在layout,错误在电路。

nch 是不可能实现b端不接地的。

找你的电路设计人员麻烦去吧。他是一神坑

可以实现,但这里肯定是接错了直接把M1_SUB接源级吗?

嗯嗯,谢谢,我试一下。

哥们,有什么这方面的资料可以推荐下吗?我的基本功还是太差了

书本上的东西都是落后的,还是多学习新工艺,多做项目就知道了,资料就是工艺厂商的drc rule,没有特别的,大部分工艺厂商的rule都差不多的

你这样画图,估计老板看到要骂人了。

哈哈,在练习中呢,不会骂的

嗯嗯好。

感觉是电路的原因

这是T的工艺吧给那啥那两个管子加单独P+然后放在NBL上就可以了

你是新手,自己搭的电路和Layerout?线路上M1M3是一个S/B节点不接GND设计,目测你的工艺nch是做不到Bulk隔离的,要么BULK接GND,要么换隔离器件。

嗯嗯,好,谢谢,这几天有事去了,没有及时看到,不好意思

嗯嗯,

谢谢大神们的指点,小弟的LVS终于过了,谢谢。

貌似我看到过好多篇这个图的请教问题了