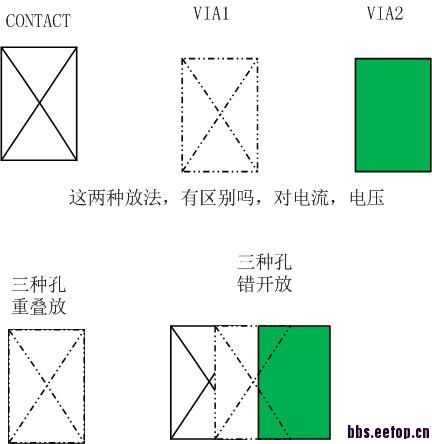

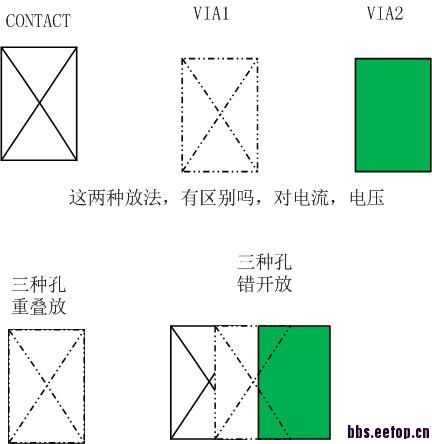

叠孔的问题,contact via1~x

时间:10-02

整理:3721RD

点击:

假如版图中 diffusion 到 metal1 metal2 metal3 。我们需要cotanctvia1 via2这三种孔完全重合的放在一起和,错开放有深区别。各有什么效果,听前辈说,有些工艺是不可以将孔重叠着放的,望高手指教

有区别

孔重叠放置,电阻相对较小。

谢谢了,但是以前有工艺不准重叠放孔,不知道你遇到过,或者知道为什么吗?

之前工艺不准重叠放孔与芯片的平坦化有关,我猜测。

想在,我所遇见的工艺里,没有这个要求。但是,会强调:孔错开放置,电阻会比较大。对某些敏感电路影响大。

楼上,并不完全如此,在引力较大的地方,以及本身就是多重叠孔时,我的建议是最好是错开放置,不然会有拉裂

芯片的风险.这种情况我遇到过

同意樓上的說法 製程和良率 考慮

谢谢 谢谢 各位前辈的耐心解答

学习了

sticking via,即使工艺支持,也会有可能影响到良率。之前的公司有颗两年多的chip被customer说low yield,最后结果就是sticking via造成的。现在的做法就是能避开尽量避开~

你们是做什么工艺的啊?0.35,0.5?还是大工艺,一般情况下,只要via不是太多都还好吧,要是比较多,电流比较大,是via错开打比较好,有个esd的专利就是要求cont,via错开打的

90-130nm,CMP工艺的问题,虽然支持sticking via。

是大片的via吗?还是由于via太少的原因?

metal1跳到metal4,每层都是4颗via,single case,但是确实很讨厌,所以我们现在都能错开就错开,可靠性可是要几年时间才能看得出来。

ok,了解了,thanks,因为我们现在内部都是叠着走的,无论是信号线之间的连接,还是power之间的连接,之前听说是要是信号线,最好是叠着走,电阻比较小,要是esd就要错开走,试验出真知啊 thanks

学习了

学习中

受益匪浅,谢谢各位前辈!

学习!